**SerDes Toolbox™**

User's Guide

# MATLAB&SIMULINK®

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

7

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

SerDes Toolbox™ User's Guide

© COPYRIGHT 2019-2023 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

#### **Revision History**

| March 2019     | Online only | New for Version 1.0 (Release 2019a)     |

|----------------|-------------|-----------------------------------------|

| September 2019 | Online only | Revised for Version 1.1 (Release 2019b) |

| March 2020     | Online only | Revised for Version 1.2 (Release 2020a) |

| September 2020 | Online only | Revised for Version 2.0 (Release 2020b) |

| March 2021     | Online only | Revised for Version 2.1 (Release 2021a) |

| September 2021 | Online only | Revised for Version 2.2 (Release 2021b) |

| March 2022     | Online only | Revised for Version 2.3 (Release 2022a) |

| September 2022 | Online only | Revised for Version 2.4 (Release 2022b) |

| March 2023     | Online only | Revised for Version 3.0 (Release 2023a) |

|                |             |                                         |

| Funda    | mentals of SerDes Systems               |

|----------|-----------------------------------------|

| Clock    | and Data Recovery in SerDes System      |

|          | hase Detector                           |

| Re       | ecovering Clock Signal                  |

| Analog   | g Channel Loss in SerDes System         |

|          | oss Model from Channel Loss Metric      |

|          | oss Model from Impulse Response         |

| In       | troducing Cross Talk                    |

|          | ge Contents of IBIS and AMI files       |

|          | ontents of IBIS File                    |

|          | ontents of AMI File                     |

|          | ustomize AMI Parameters                 |

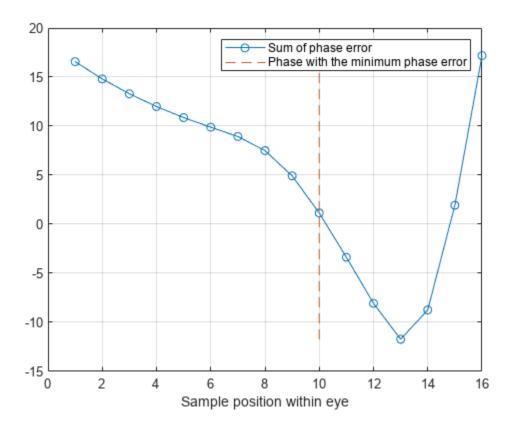

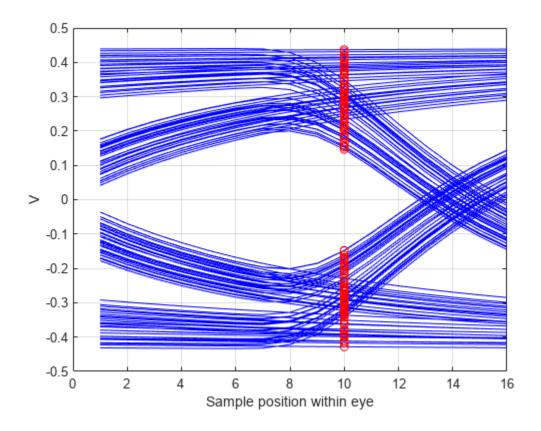

|          | efine Clock Position in Statistical Eye |

|          | AMn Capabilities                        |

| Statist  | cical Analysis in SerDes Systems        |

| In       | it Subsystem Workflow                   |

| Se       | erDes System Using Init Subsystem       |

|          | AMn Thresholds                          |

|          | dvance Init Options                     |

| M        | letrics Used in Statistical Analysis    |

| Sitter A | Analysis in SerDes Systems              |

| Linux `  | Version Compatibilities                 |

|          |                                         |

|          | Customize SerDes Systems To             |

|          | Create and Customize 1D15-AMI Models 10                                                       | hic2 |

|----------|-----------------------------------------------------------------------------------------------|------|

| 3        |                                                                                               |      |

|          | SiSoft Link                                                                                   | 3-2  |

|          | SerDes Toolbox Interface for SiSoft Quantum Channel Designer and QSI Software                 | 3-3  |

|          | Signal Integrity Link                                                                         | 3-11 |

| L        | Design and Simulate SerDes Systems Exam                                                       | ples |

| •        | Find Zeros, Poles, and Gains for CTLE from Transfer Function                                  | 4-2  |

|          | Convert Scattering Parameter to Impulse Response for SerDes System                            | 4-21 |

|          | Globally Adapt Receiver Components Using Pulse Response Metrics to Improve SerDes Performance | 4-27 |

|          | Globally Adapt Receiver Components in Time Domain                                             | 4-32 |

|          | Model Clock Recovery Loops in SerDes Toolbox                                                  | 4-52 |

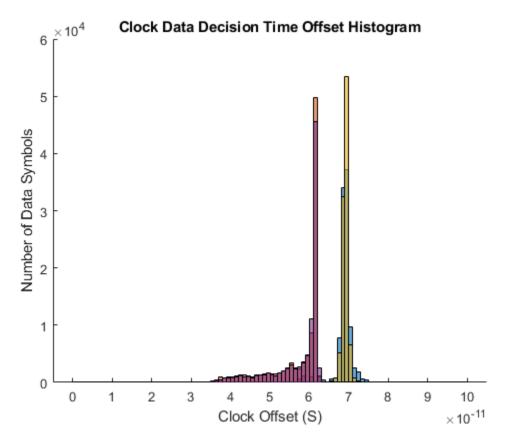

|          | Phase Detectors: Baud-Rate Type-A versus Bang-Bang                                            | 4-78 |

| , [      | Customize SerDes Syst                                                                         | ems  |

|          | Customizing SerDes Toolbox Datapath Control Signals                                           | 5-2  |

|          | Customizing Datapath Building Blocks                                                          | 5-14 |

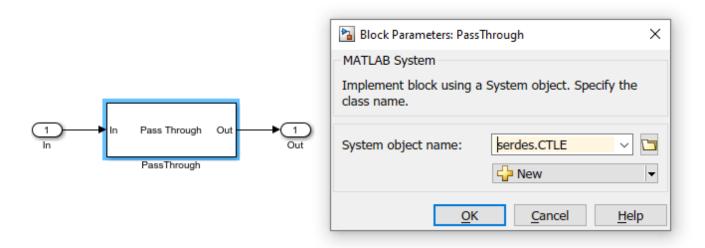

|          | Implement Custom CTLE in SerDes Toolbox PassThrough Block                                     | 5-28 |

|          | Step Response Based CTLE                                                                      | 5-37 |

| ļГ       | Customize IBIS-AMI Mo                                                                         | dels |

| <b>7</b> | Managing AMI Parameters                                                                       | 6-2  |

|          | Design IRIS-AMI Models to Support Clock Forwarding                                            | 6-18 |

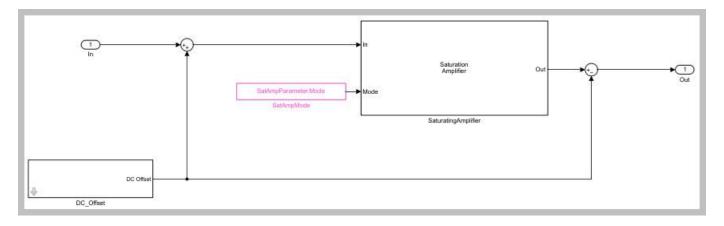

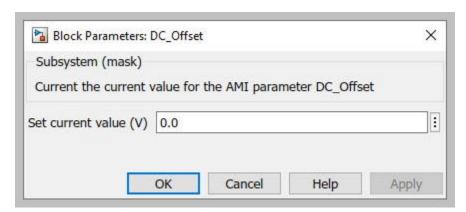

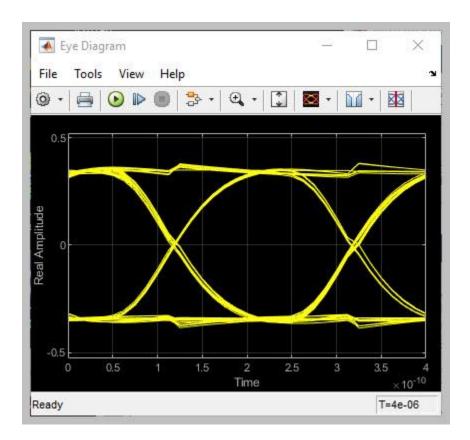

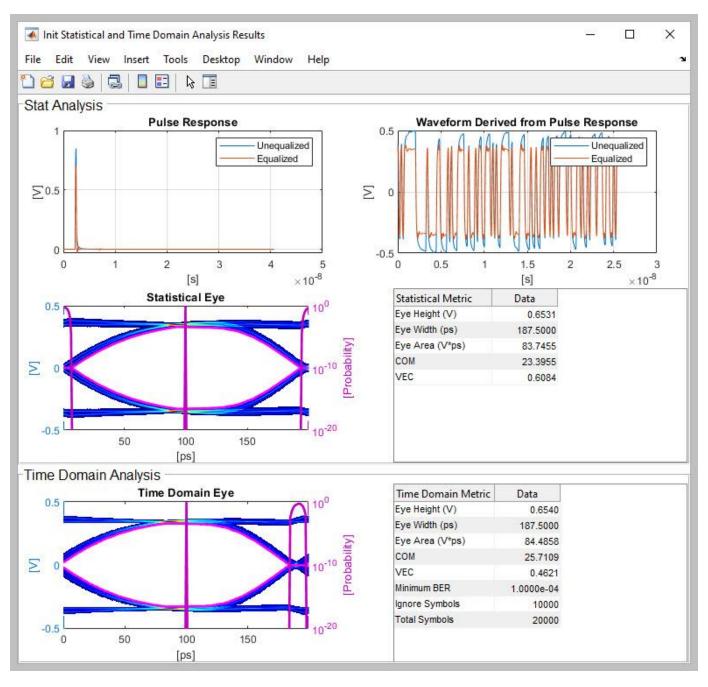

|   | Design IBIS-AMI Models to Support DC Offset                         | <b>6-3</b> 3 |

|---|---------------------------------------------------------------------|--------------|

|   | Simulate Crosstalk Cancellation in IBIS AMI Receiver Models         | 6-41         |

|   | Design IBIS-AMI Models to Support Rx Decision Time                  | 6-47         |

|   |                                                                     |              |

|   | Industry Standard IBIS-AMI M                                        | odels        |

| 7 |                                                                     |              |

|   | PCIe4 Transmitter/Receiver IBIS-AMI Model                           | 7-2          |

|   | PCIe5 Transmitter/Receiver IBIS-AMI Model                           | 7-16         |

|   | DDR5 SDRAM Transmitter/Receiver IBIS-AMI Model                      | 7-38         |

|   | DDR5 Controller Transmitter/Receiver IBIS-AMI Model                 | 7-50         |

|   | CEI-56G-LR Transmitter/Receiver IBIS-AMI Model                      | 7-61         |

|   | USB 3.1 Transmitter/Receiver IBIS-AMI Model                         | 7-70         |

|   | Design DDR5 IBIS-AMI Models to Support Back-Channel Link Training   | 7-79         |

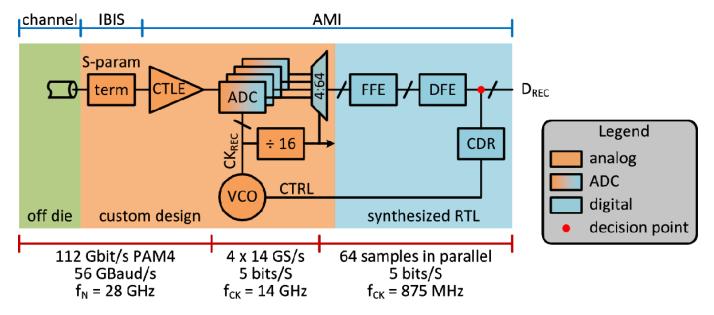

|   | ADC IBIS-AMI Model Based on COM                                     | 7-111        |

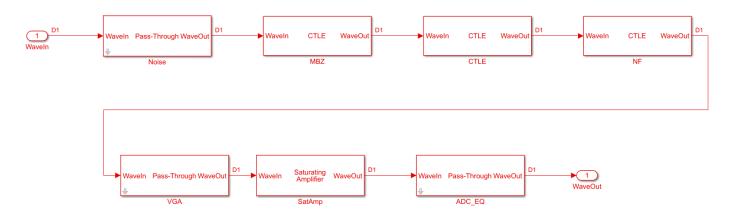

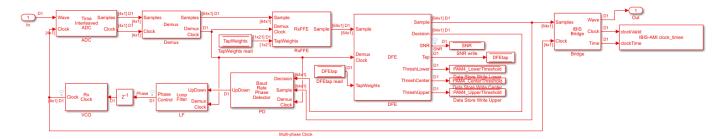

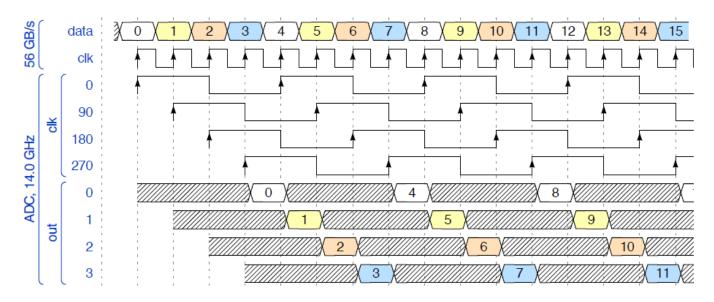

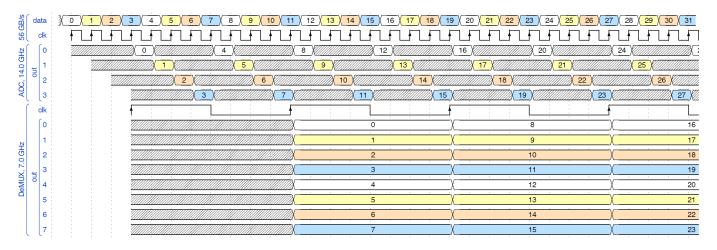

|   | Architectural 112G PAM4 ADC-Based SerDes Model                      | 7-126        |

|   | Architectural 100G Dual-Summing-Node-DFE PAM4 SerDes Receiver Model | 7-136        |

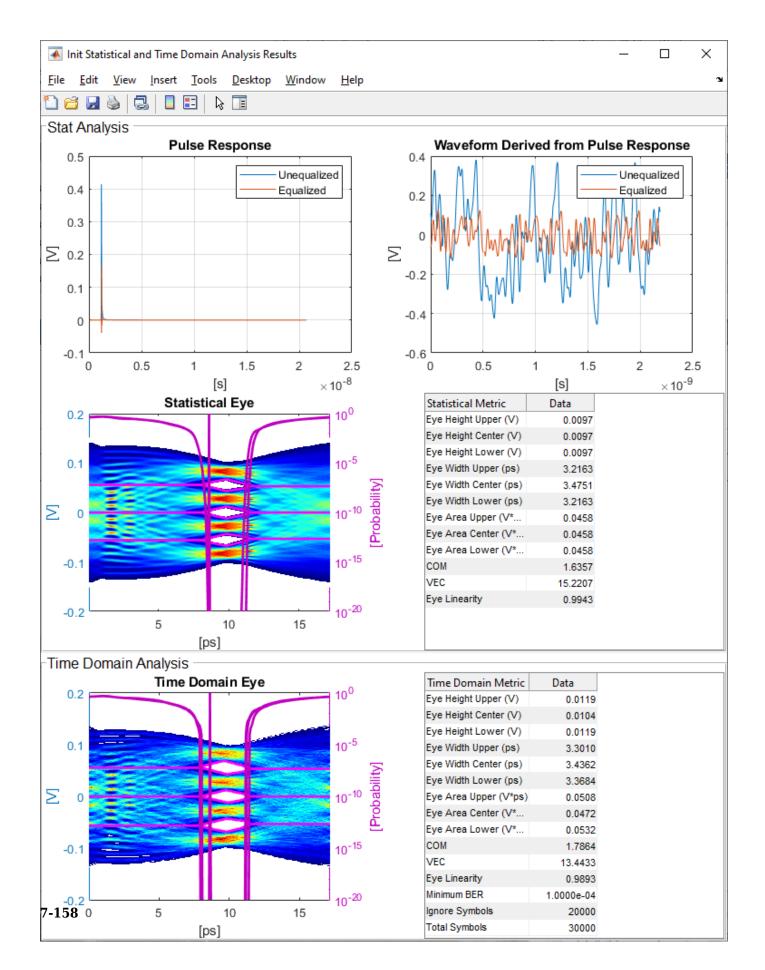

|   | CEI-112G-VSR Transmitter/Receiver IBIS-AMI Model                    | 7-150        |

|   | USB4 V2 Transmitter/Receiver IBIS-AMI Model                         | 7-163        |

## **Design and Simulate SerDes System Topics**

- "Fundamentals of SerDes Systems" on page 1-2

- "Clock and Data Recovery in SerDes System" on page 1-3

- "Analog Channel Loss in SerDes System" on page 1-14

- "Manage Contents of IBIS and AMI files" on page 1-16

- "Statistical Analysis in SerDes Systems" on page 1-19

- "Jitter Analysis in SerDes Systems" on page 1-26

- "Linux Version Compatibilities" on page 1-29

## **Fundamentals of SerDes Systems**

Modern high-speed electronic systems are characterized by increased data speed integrated circuits (ICs). The input/output performance remains the bottleneck that limits the overall performance of a high-speed system. Serial data transfer is the most efficient way of communicating large data quickly between computer chips on printed circuit boards through copper cables and through short, medium, and long length fiber optics.

Thus, many systems now aggregate and serialize multiple input/output (I/O) signals for transmission across fiber and copper cables and PCBs at a higher data rate, recovering and de-serializing the individual signals on the receiving end. These SerDes (Serializer/De-Serializer) implementations employ additional silicon real estate to perform sophisticated equalization required for reliable signal transmission at very high data speeds. This approach helps maximize throughput at the system level.

SerDes design is a complex, iterative process that typically starts with a baseline SerDes system that demonstrates the feasibility of a design approach. This system also establishes budgets for the different parts of the serial channel and associated transmitter (TX) and receiver (RX) equalization circuitry. The data that describes the desired behavior of each of the equalization filters in both the transmitter and the receiver is then back-annotated in the behavioral models with the correlation with simulations or measurements. The final step is to implement the training algorithms and control loops that will be executed by the chip during startup and from time to time when the channel needs to be retrained.

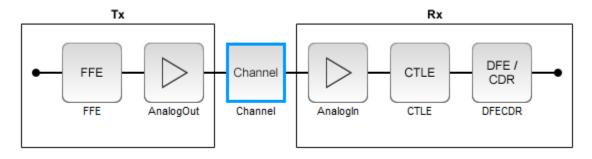

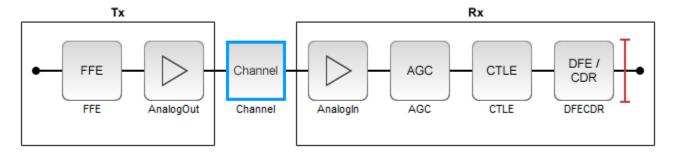

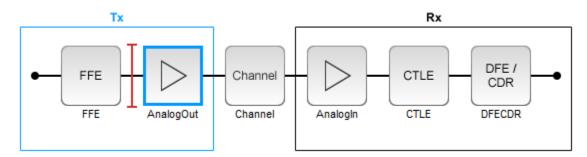

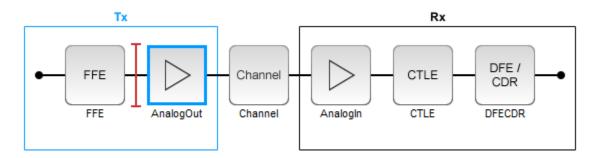

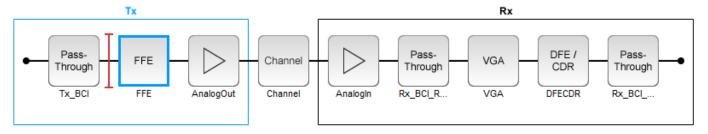

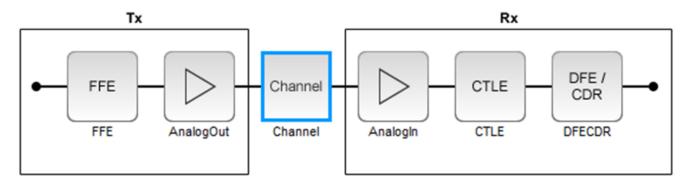

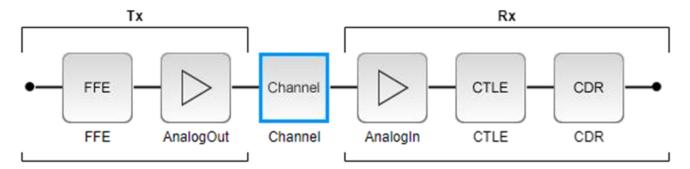

There are six sections of a SerDes system:

- TX equalization This becomes the IBIS-AMI dll for the transmitter.

- TX AnalogOut This becomes the analog model of the transmitter. It is part of the IBIS model for TX, and is typically represented by the I-V and V-T characteristics curves in the .ibs file.

- Channel This becomes the model of the physical channel, including the TX and RX package models.

- RX AnalogOut This becomes the analog model of the receiver. It is part of the IBIS model for RX, and is typically represented by the I-V and V-T characteristics curves in the .ibs file.

- RX equalization This becomes the IBIS-AMI dll for the receiver.

- Training algorithms and control loops These become the on-chip microcode that is executed inside of the chip during startup and when the channel needs to be retrained.

#### See Also

#### **More About**

"Design SerDes System and Export IBIS-AMI Model"

## **Clock and Data Recovery in SerDes System**

#### In this section...

"Phase Detector" on page 1-3

"Recovering Clock Signal" on page 1-6

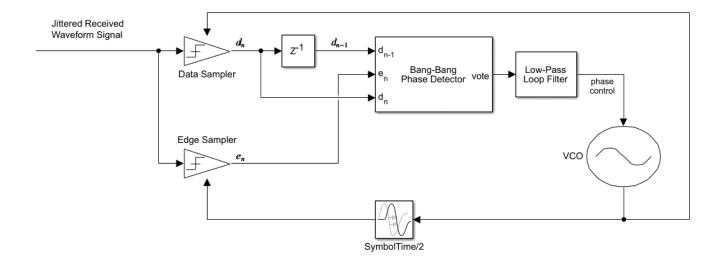

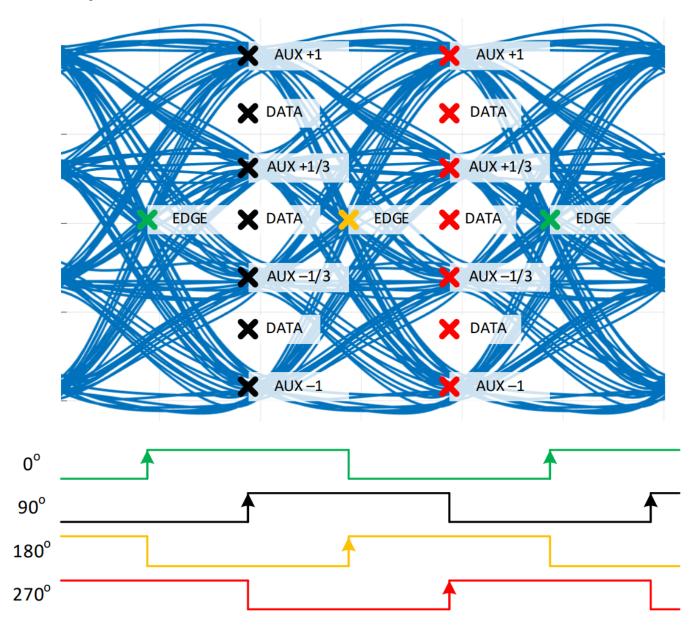

High-speed analog SerDes systems use clock and data recovery (CDR) circuitry to extract the proper time to correctly sample the incoming waveform. The CDR circuitry creates a clock signal that is aligned to the phase and to some extent the frequency of the transmitted signal. Phase tracking (first order CDR) is usually accomplished by using a nonlinear bang-bang or Alexander phase detector that drives a voltage-controlled oscillator (VCO). Frequency tracking (second order CDR) integrates any remaining phase errors and compensates for gross differences between the transmitter reference clock and the receiver reference clock. serdes.CDR and serdes.DFECDR use the first-order CDR algorithm.

#### **Phase Detector**

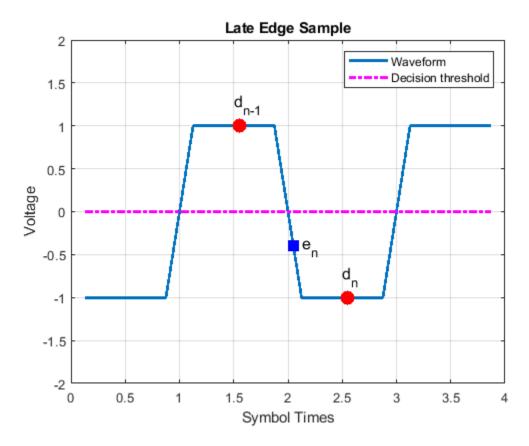

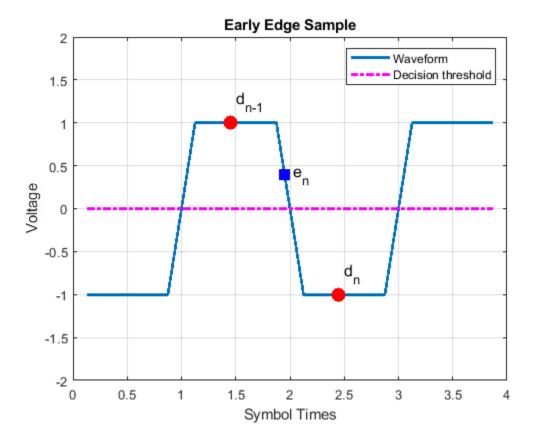

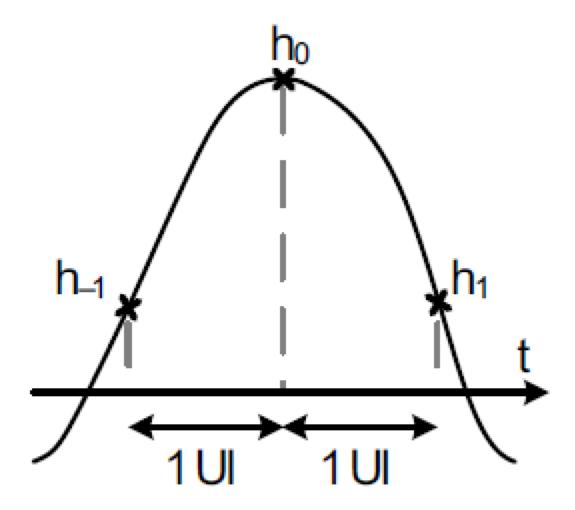

The Alexander or bang-bang phase detector samples the received waveform at the edge and middle of each symbol. The edge sample  $(e_n)$  and data samples  $(d_{n-1}$  and  $d_n)$  are processed with some digital logic to determine if the edge sample, and thus the clock phase, is early or late. The edge sample,  $e_n$ , and data sample,  $d_n$ , are separated by half of a symbol time.

Consider the waveform where a data transition has occurred, and both  $e_n$  and  $d_n$  are below the decision threshold voltage. The binary values resolved from  $e_n$  and  $d_n$  match, which indicates the clock phase is late.

Similarly, when the binary values resolved from  $\mathbf{e}_n$  and  $\mathbf{d}_{n\text{-}1}$  match, the clock phase is early.

Representing the binary output of the sampler by  $\pm 1$ , the behavior of the phase detector for NRZ or PAM4 modulation is summarized here:

| d <sub>n-1</sub> | e <sub>n</sub> | d <sub>n</sub> | Action                                          |

|------------------|----------------|----------------|-------------------------------------------------|

| -1               | -1             | 1              | Clock phase is early. Shift phase to the right. |

| 1                | 1              | -1             |                                                 |

| -1               | 1              | 1              | Clock phase is late. Shift phase to the left.   |

| 1                | -1             | -1             |                                                 |

| -1               | X              | -1             | No action is necessary.                         |

| 1                | X              | 1              |                                                 |

For PAM3 modulation, the symbol levels are -0.5, 0, and 0.5. The default threshold levels (th) are  $\pm 0.25$ . The modified truth table thus become:

| d <sub>n-1</sub> | e <sub>n</sub> | d <sub>n</sub> | Action |

|------------------|----------------|----------------|--------|

|                  | $ e_n>-th$     | 0              | late   |

|                  | $e_n < -th$    | 0              | early  |

|                  | $e_n > 0$      | 0.5            | late   |

| -0.5             | $e_n < 0$      | 0.5            | early  |

| 0                | $e_n > th$     | 0.5            | late   |

| d <sub>n-1</sub> | e <sub>n</sub> | d <sub>n</sub> | Action |

|------------------|----------------|----------------|--------|

| 0                | $e_n < th$     | 0.5            | early  |

| 0                | $e_n > -th$    | -0.5           | early  |

| 0                | $e_n < -th$    | -0.5           | late   |

| 0.5              | $e_n > th$     | 0              | early  |

|                  | $e_n < th$     | 0              | late   |

|                  | $e_n > 0$      | -0.5           | early  |

| 0.5              | $e_n < 0$      | -0.5           | late   |

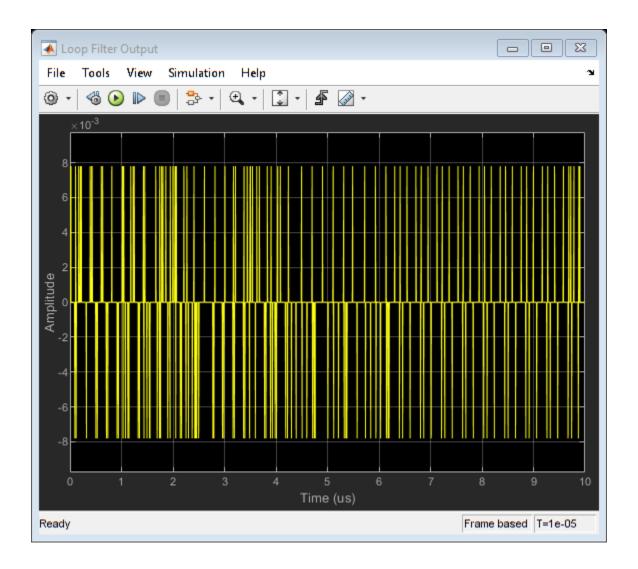

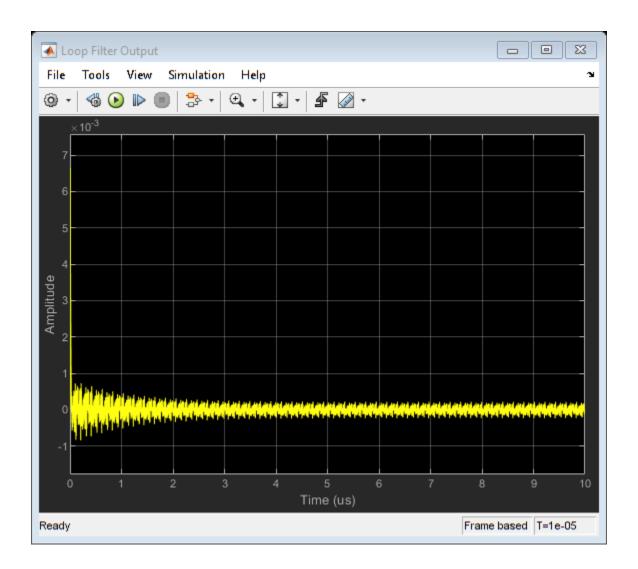

Driving the VCO directly from the phase detector output results in excessive clock jitter. To eliminate the jitter, the output of the phase detector is lowpass filtered by accumulating it in a vote. When the accumulated vote exceeds a specific count threshold, the phase of the VCO is incremented or decremented.

## **Recovering Clock Signal**

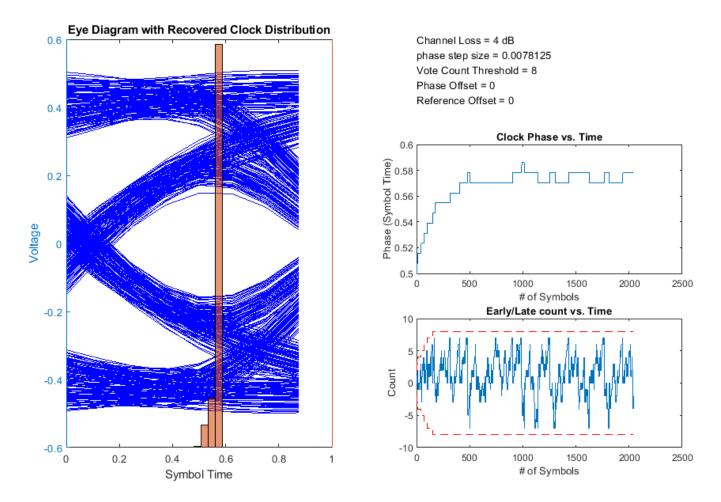

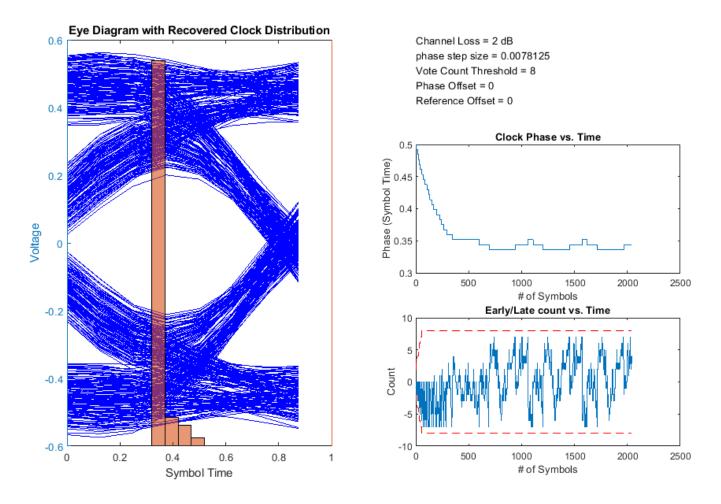

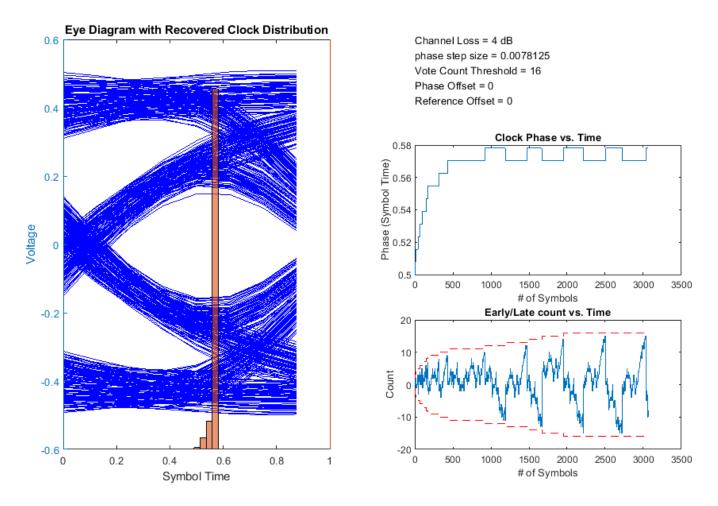

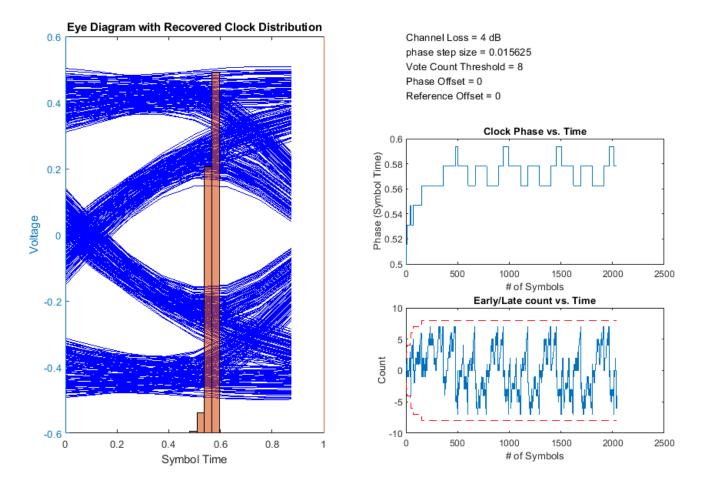

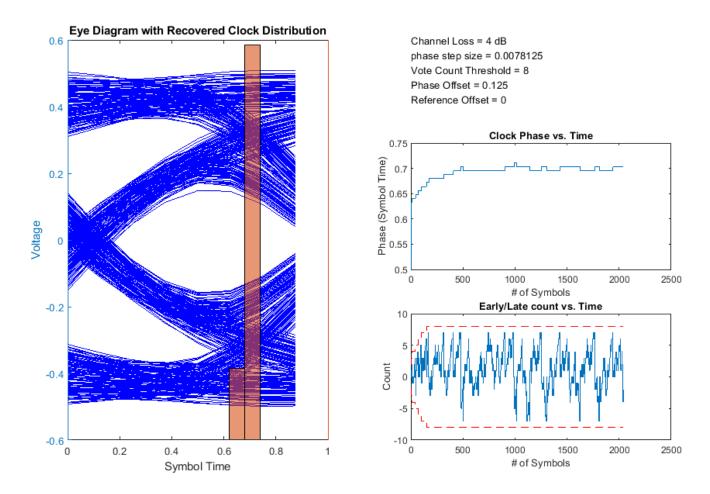

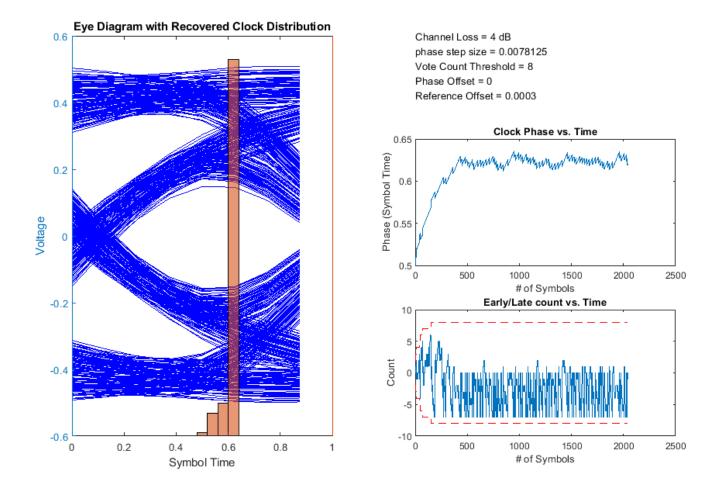

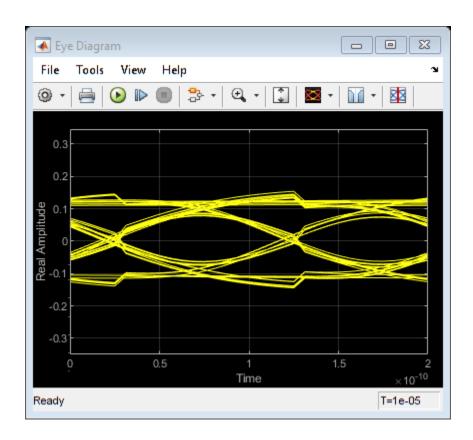

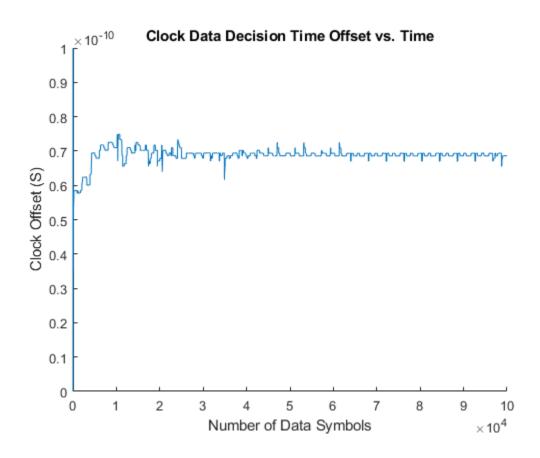

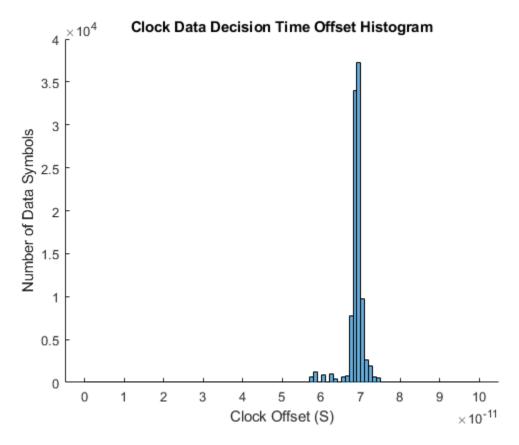

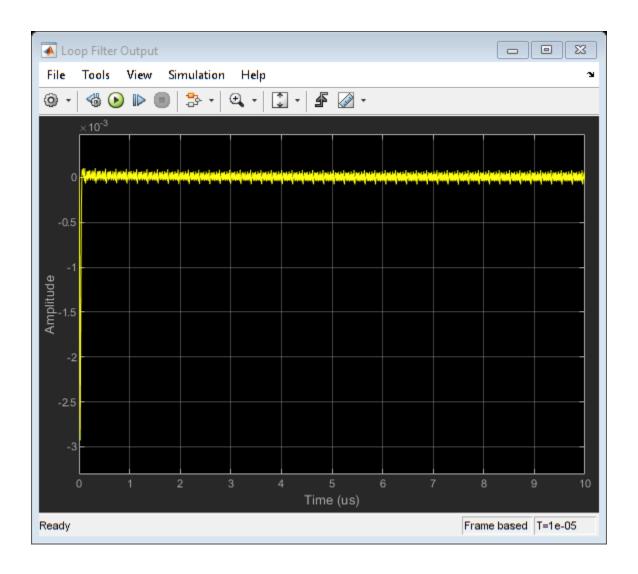

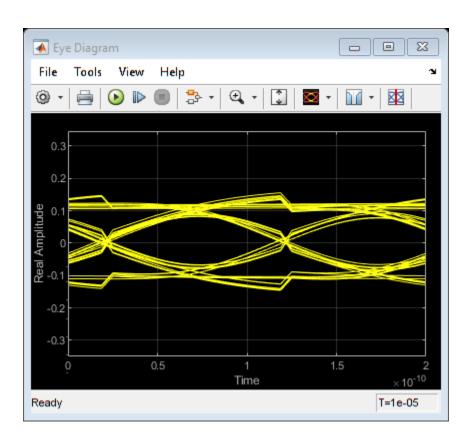

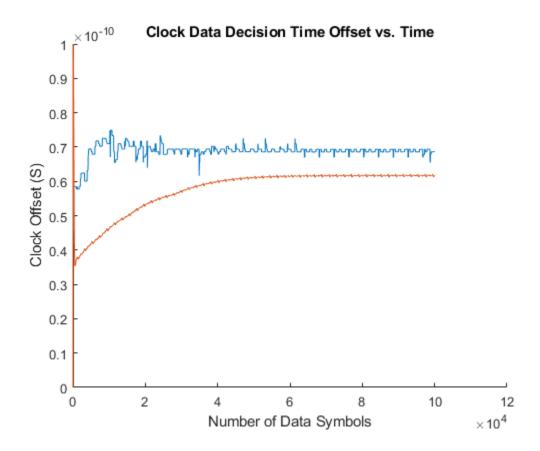

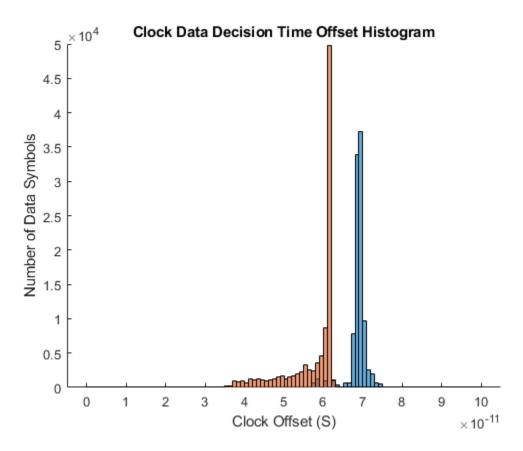

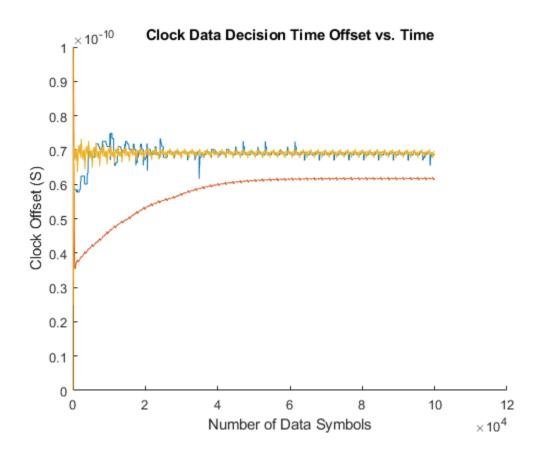

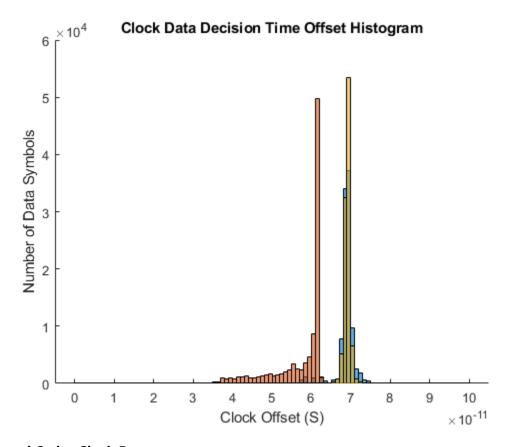

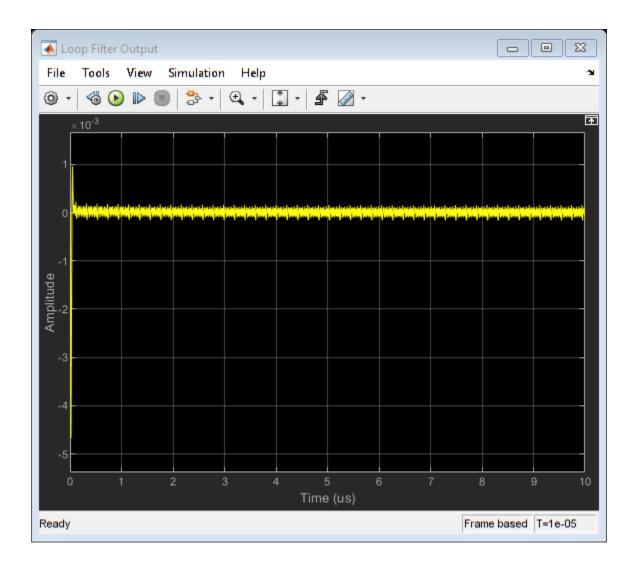

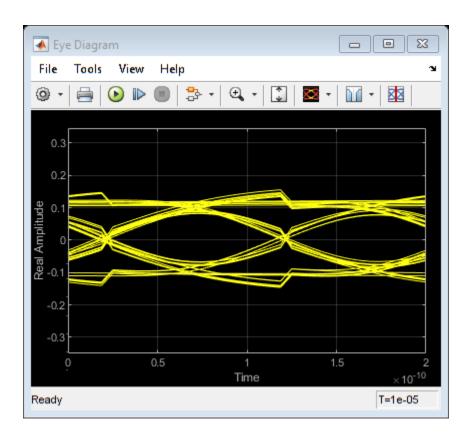

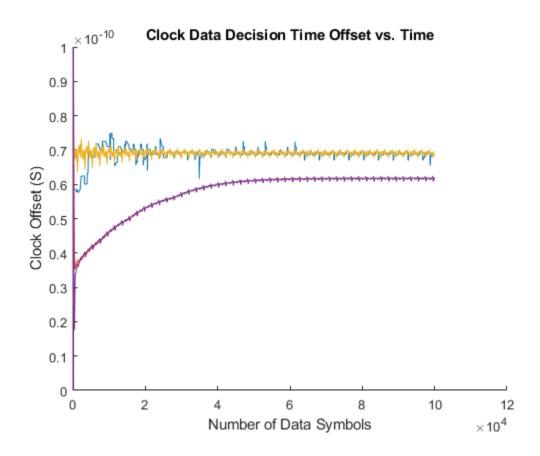

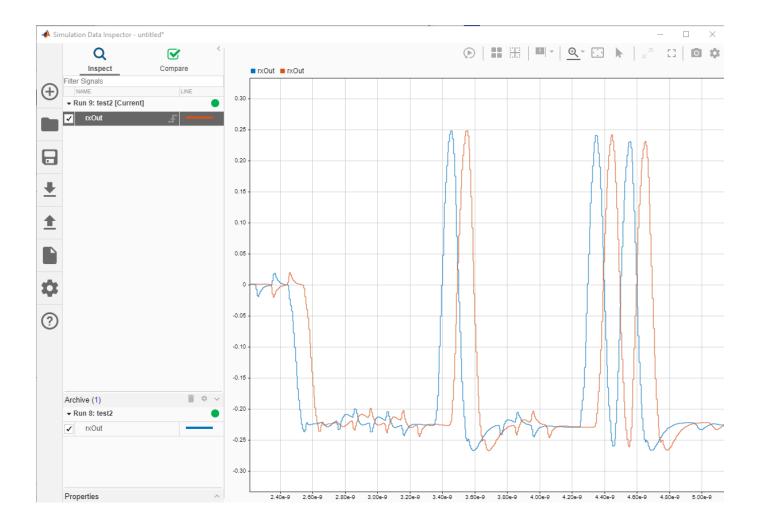

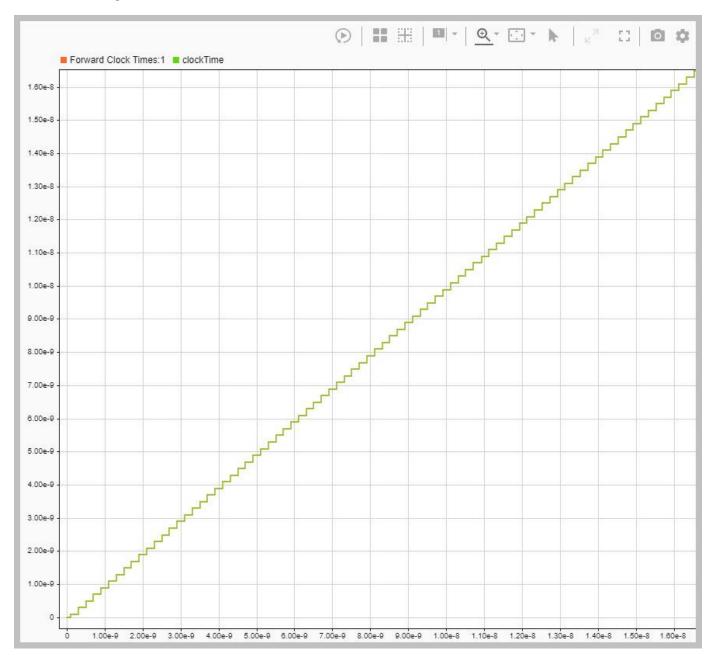

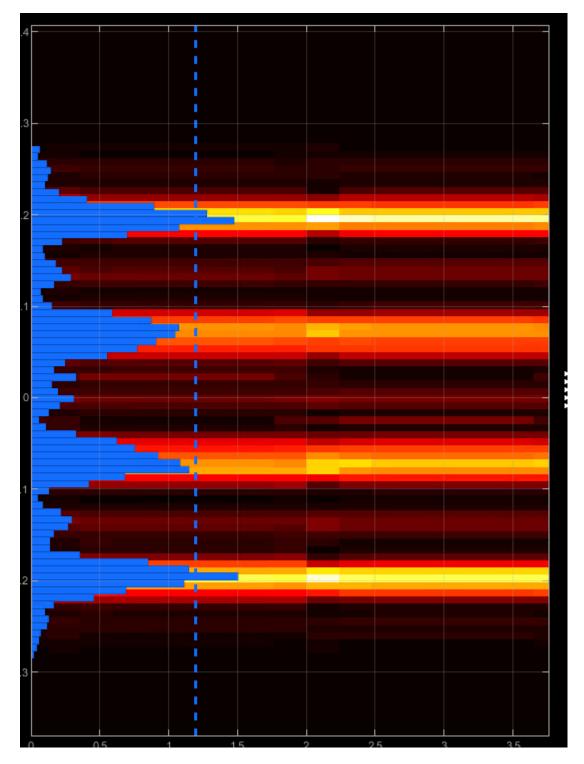

Recover the clock signal from a repeating pseudorandom binary sequence (PRBS9) nonreturn to zero (NRZ) signal. Consider the channel has 4 dB loss, the phase step size is  $\frac{1}{128}$ , the vote count threshold is 8, and that there are no phase or reference offsets.

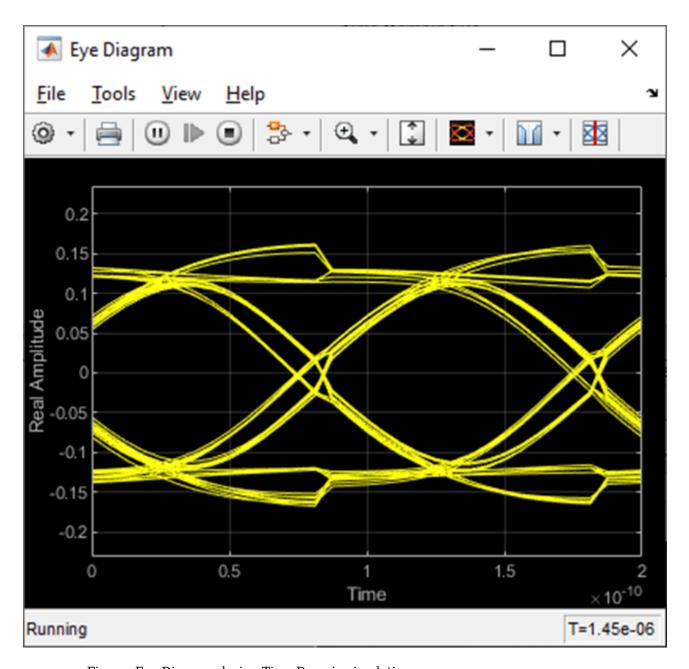

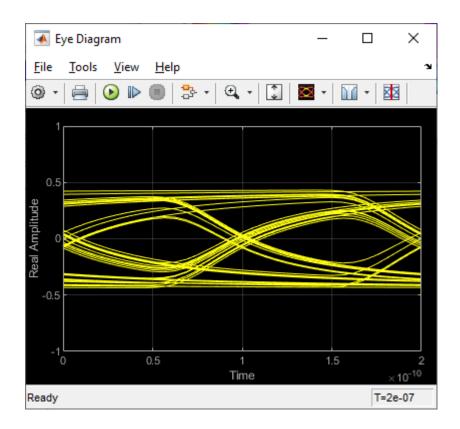

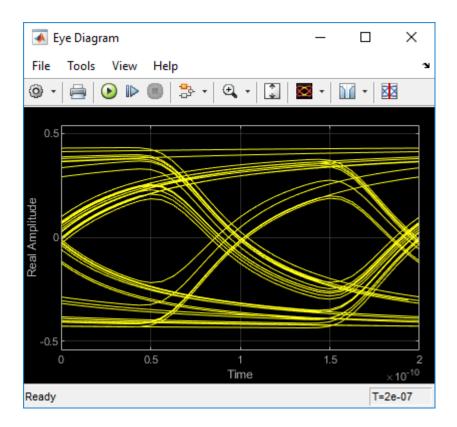

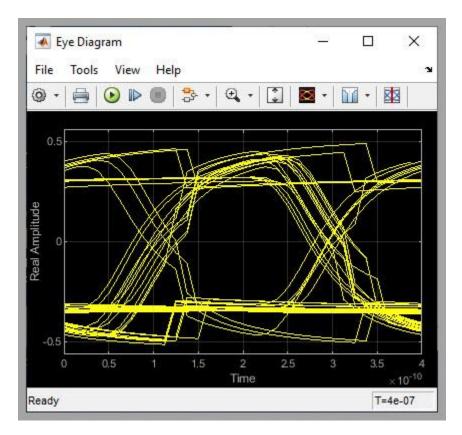

The baseline behavior is shown with the eye diagram and the resulting clock probability distribution function (PDF). The PDF is very near the center of the eye. The clock phase settles between a value of 0.5703 symbol time and 0.5781 symbol time. The dithering between the two values is a consequence of the nonlinear bang-bang phase detector and is the source of CDR hunting jitter. To reduce the magnitude of dithering, reduce the phase step size. To reduce the period of dithering, reduce the vote count threshold.

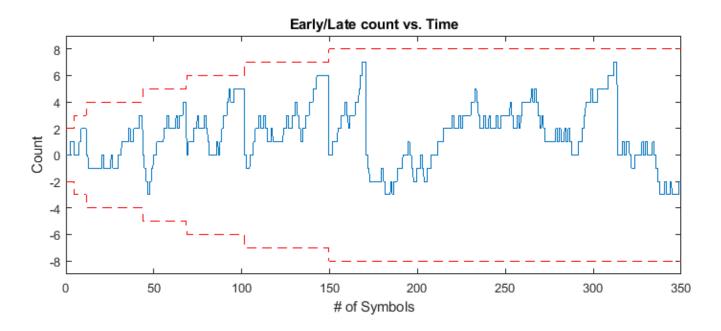

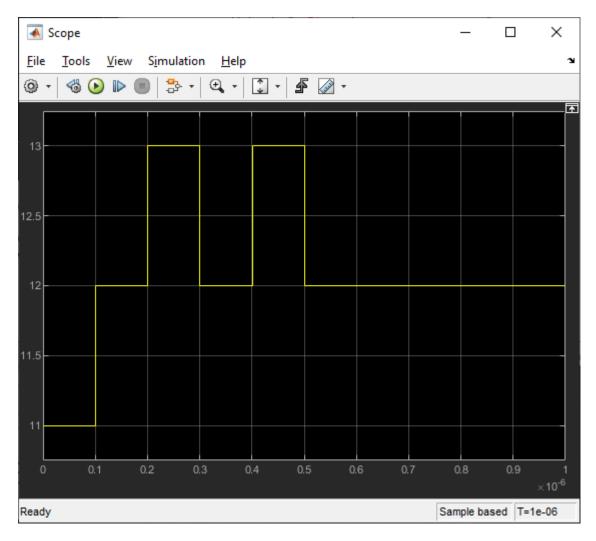

The output of the phase detector is accumulated in the early/late vote count. When the count exceeds the vote count threshold, the phase is incremented or decremented. To accelerate CDR convergence, the count threshold starts at 2, and each time the magnitude of the vote exceeds the threshold, the threshold is incremented until it reaches the maximum count. This figure shows the first 350 symbols of the early/late count (blue) and the threshold (dashed red line). Internal to the CDR block, the vote is incremented or decremented, checked against the threshold and then reset if necessary. The external vote value shown in figure below does not touch the threshold but is evident when the vote is reset to 0.

To show the clock converging to a different phase, change the channel loss to  $2\ dB$ . The clock phase now adapts to around  $0.35\ symbol$  time.

Increasing the vote count threshold to 16 results in a larger dithering period.

Increasing the phase step size to  $\frac{1}{64}$  increases the dithering magnitude.

Manually shifting the data sampler location when the equalized eye does not display left/right symmetry can maximize the eye height. For example, shift the clock phase to the right by  $\frac{1}{8}$  of a symbol time to shift the output clock phase from 0.57 symbol time to 0.7 symbol time.

You can also inject a small amount of reference clock frequency offset impairment to implement a more realistic CDR.

#### References

- [1] Sonntag, J. L. and Stonick, J. "A Digital Clock and Data Recovery Architecture for Multi-Gigabit/s Binary Links." *IEEE Journal of Solid-State Circuits*, 2006.

- [2] Razavi, B. "Challenges in the design high-speed clock and data recovery circuits." *IEEE Communications Magazine*, 2002.

#### See Also

serdes.CDR | serdes.DFECDR | DFECDR | CDR

## **Analog Channel Loss in SerDes System**

#### In this section...

"Loss Model from Channel Loss Metric" on page 1-14

"Loss Model from Impulse Response" on page 1-14

"Introducing Cross Talk" on page 1-14

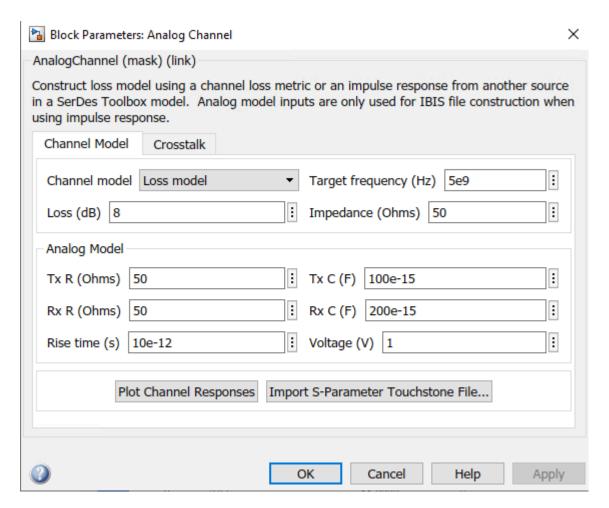

Limiting factors in high-speed data transmission includes cross talk, attenuation, and reflection noise. The Analog Channel block and serdes. ChannelLoss System object  $^{\text{\tiny M}}$  parameterize a channel model that represents a lossy transmission line typical in high-speed SerDes application. The loss model is constructed either from a parameterized channel loss model or from an impulse response from another source.

#### **Loss Model from Channel Loss Metric**

A discrete time, band-limited analog impulse response characterizes the serdes. ChannelLoss System object. It represents the response of a system to an impulse response vector with an impulse magnitude of  $\frac{1}{dt}$ , where dt is the sample interval.

To calculate the impulse response, serdes. ChannelLoss first calculates the S-parameter component S21 according to channel loss at frequencies ranging from 0 to  $f_{\rm max}$ , maximum frequency of interest, where  $f_{\rm max} = \frac{1}{dt}$ . This is done by determining the loss at the target frequency, and then linearly extrapolating required channel length to achieve target channel loss. Then transmitter and receiver termination S-parameter are then calculated according to the equations 93A-17 and 93A-18 from the IEEE 802.3bi-2014 specifications [1].

After calculating S21, the System object adds the negative frequency data points based on the expected even symmetry of the real components of S21 and the odd symmetry of the imaginary components of S21 of the frequency response. The impulse response is calculated from the inverse Fourier transform of S21. Finally, the impulse response is resampled so that the sample interval is dt.

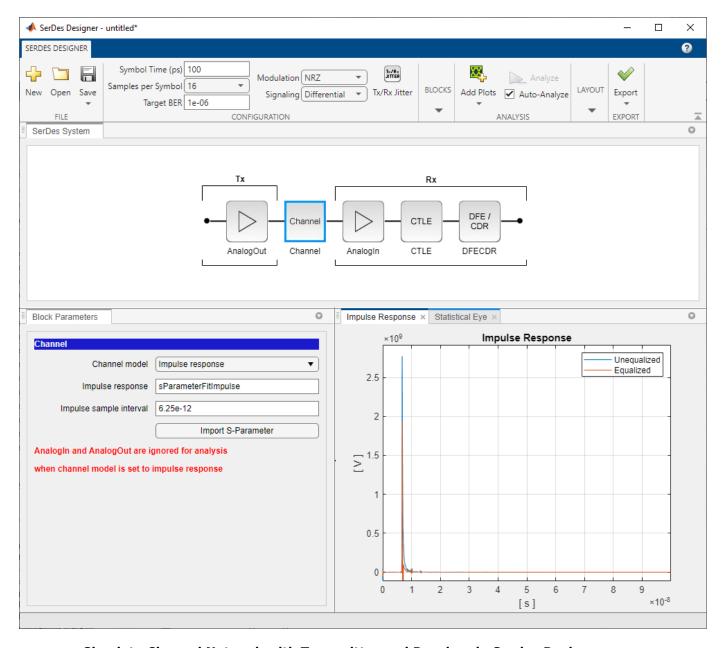

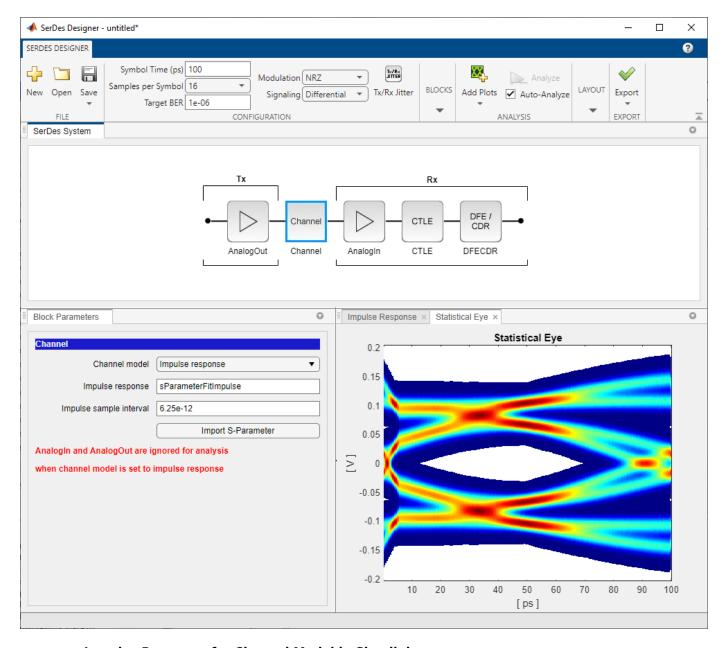

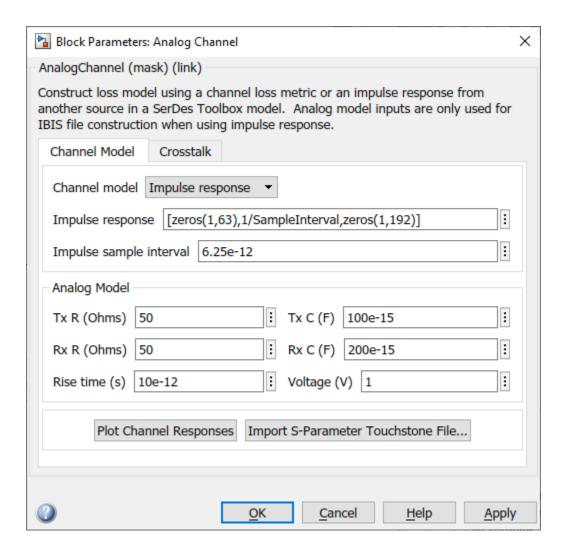

## **Loss Model from Impulse Response**

To construct a loss model from an impulse response vector, input the impulse response vector from another source. You can also define the impulse sample interval. Changing the symbol time and number of samples per symbol changes the data rate of the SerDes system.

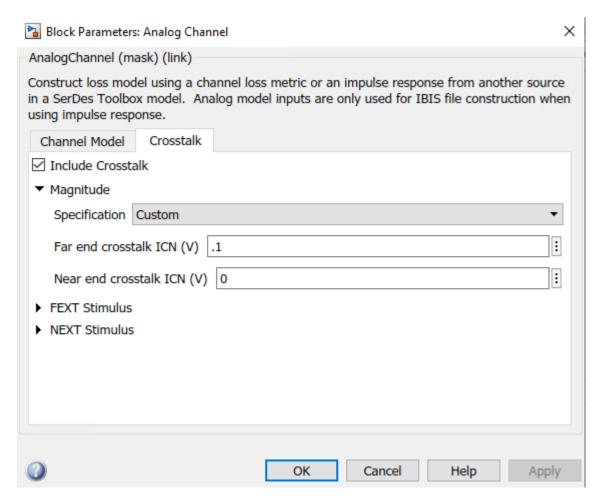

## **Introducing Cross Talk**

You can include crosstalk in your simulation from the **SerDes Designer** app, or using the Analog Channel block in Simulink $^{\otimes}$ . If the parameterized channel loss model is used, you can specify the strength of the near and far end crosstalk aggressors according to specification standards or you can specify your own custom integrated crosstalk noise (ICN) levels. If a custom impulse response is used, then up to 6 additional columns can be used to represent the crosstalk impulse response. For more information, see Analog Channel and serdes. Channel Loss.

## References

[1] IEEE 802.3bj-2014. "IEEE Standard for Ethernet Amendment 2: Physical Layer Specifications and Management Parameters for 100 Gb/s Operation Over Backplanes and Copper Cables." https://standards.ieee.org/standard/802\_3bj-2014.html.

## **See Also**

Analog Channel | serdes.ChannelLoss | SerDes Designer

## Manage Contents of IBIS and AMI files

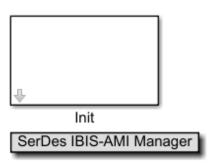

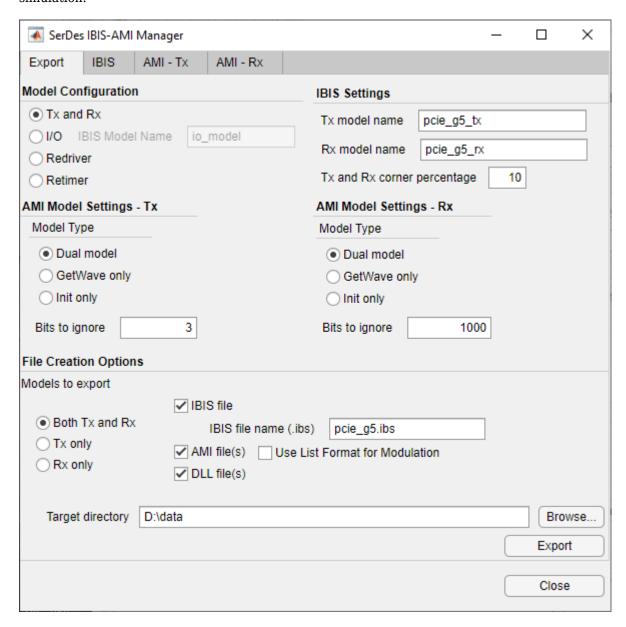

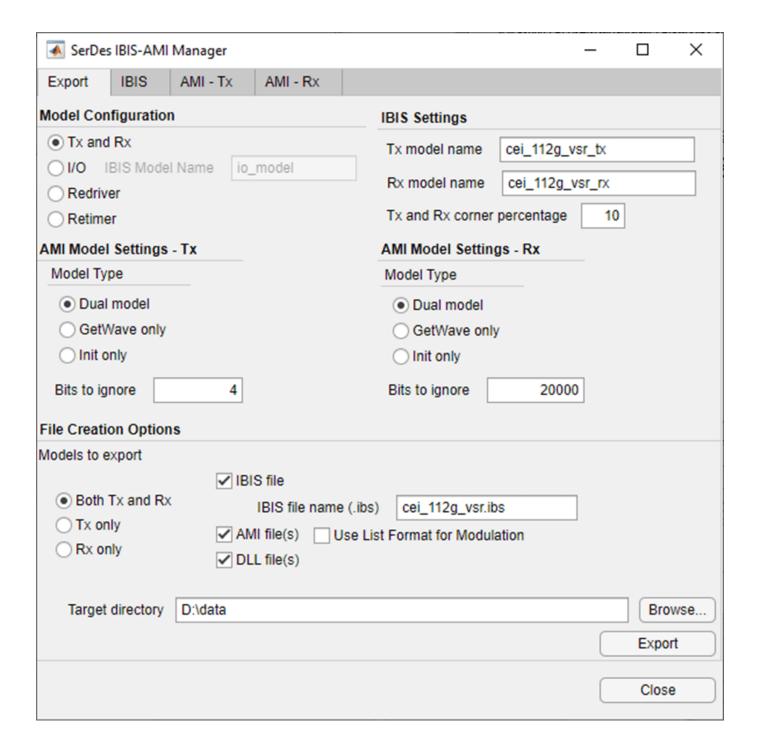

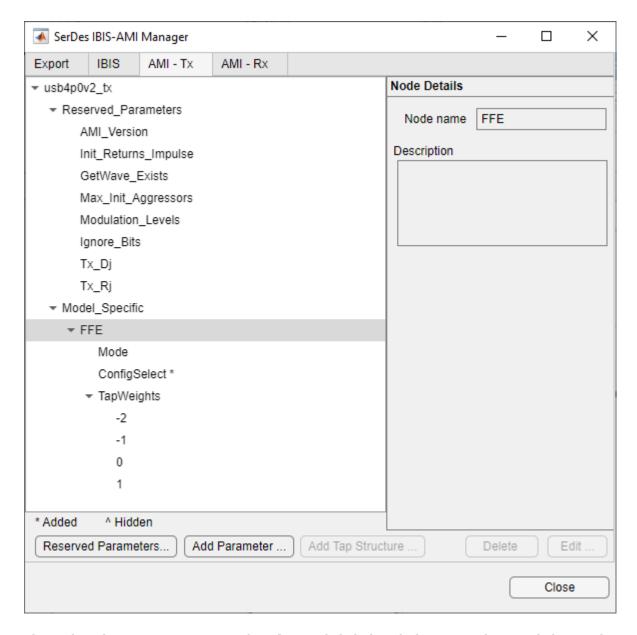

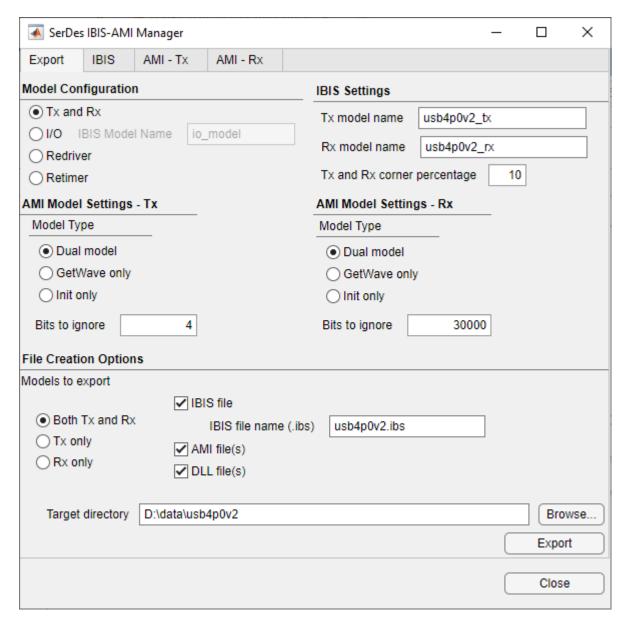

You can manage the IBIS-AMI parameters by opening the SerDes IBIS-AMI Manager dialog box from the Configuration block.

#### Contents of IBIS File

The **IBIS** tab in the SerDes IBIS-AMI Manager dialog box defines the content of the IBIS file. Set the parameters used to define the IBIS file in the AnalogOut and AnalogIn blocks in the **SerDes Designer** app and in the **IBIS** tab in the SerDes IBIS-AMI Manager.

From the transmitter side in the AnalogOut block:

- **Voltage (V)** Typical value of voltage range in the IBS file.

- **R (Ohms)** Slope of the typical pull-up and pull-down IV curves in the IBS file.

- **C** (**pF**) Typical value of the **C** comp in the IBS file.

From the receiver side in the AnalogIn block:

- **Voltage (V)** Typical value of voltage range in the IBS file.

- **R (Ohms)** Slope of the typical ground clamp IV curve in the IBS file.

- C (pF) Typical value of the C\_comp in the IBS file.

You can only enter the typical values for these parameters. You can define the **Tx and Rx corner percentage** in the **Export** tab of the SerDes IBIS-AMI Manager dialog box. The minimum and maximum values are generated by subtracting or adding to the typical value its fractional corner percentage.

The performance of an input/output (I/O) buffer is a function of process, voltage, and temperature (PVT). There are 27 PVT corners. IBIS supports three model corners: Typ, Min, and Max. When generating the IBIS file, the **Voltage (V)**, **R (Ohms)**, and **C (pF)** values are used for the Typ corner.

- Min refers to the slow/weak corner. It groups slow process, low voltage, and high temperature. The voltage and resistance are decreased and the capacitance is increased for the Min corner.

- Max refers to the fast/strong corner. It groups fast process, high voltage, and low temperature.

The voltage and resistance are increased and the capacitance is decreased for the Max corner.

You can also specify the IBIS-AMI model in the **Export** tab of the SerDes IBIS-AMI Manager dialog box as single I/O, redriver, or retimer. Selecting these model configurations changes the contents of the IBIS file.

- If you select I/O as the model configuration, the IBIS model is reconfigured to a single model of Model Type I/O.

- If you select **Retimer** or **Redriver** as the model configuration, the components of the IBIS file is updated to include the repeater pins.

#### **Contents of AMI File**

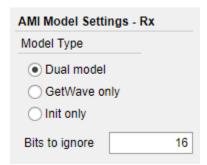

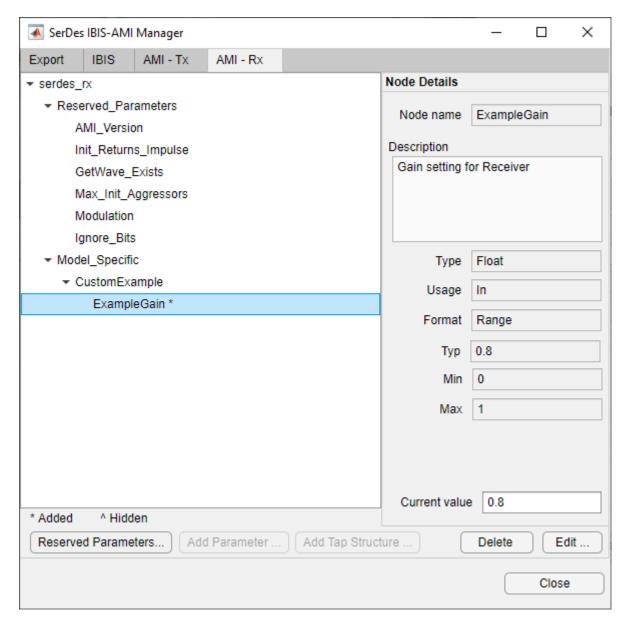

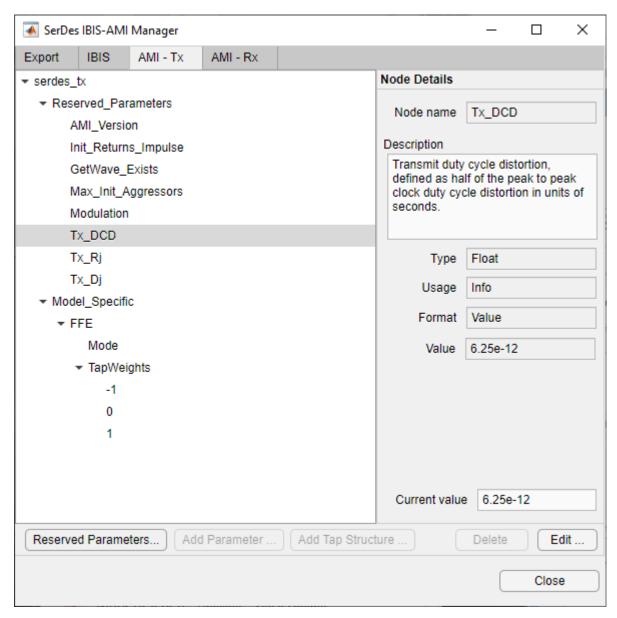

The AMI - Tx and AMI - Rx tabs in the SerDes IBIS-AMI Manager dialog box define the content of the AMI file. They contain the required and commonly used reserved AMI parameters. You can also define the model-specific parameters for the relevant blocks.

There are five Reserved Parameters included in every AMI file generated by the SerDes Toolbox:

- **AMI\_Version** IBIS version supported by the model

- **Init Returns Impulse** whether the model supports statistical simulation or not

- **GetWave Exists** whether the model supports time-domain simulation or not.

- Max\_Init\_Aggressors the number of crosstalk aggressors supported by the model

- **Modulation** the modulation scheme of the model.

- **Ignore\_Bits** the number of bits ignored during time domain analysis.

If you select **Retimer** or **Redriver** as the model configuration in the **Export** tab of the SerDes IBIS-AMI Manager dialog box, an additional Reserved\_Parameter **Repeater\_Type** is added to the **AMI - Rx** tab. This parameter specifies the type of the repeater.

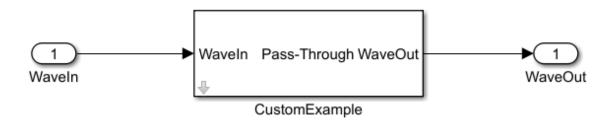

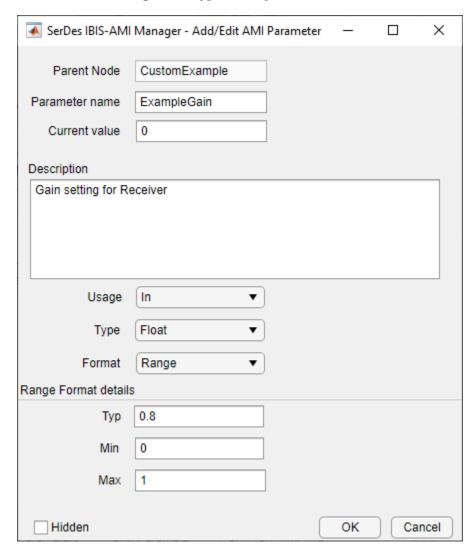

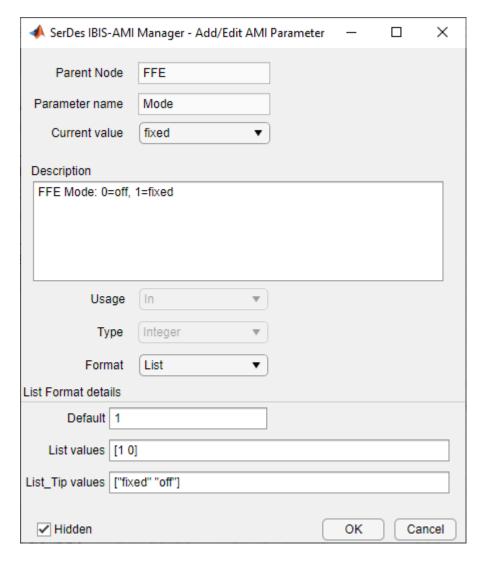

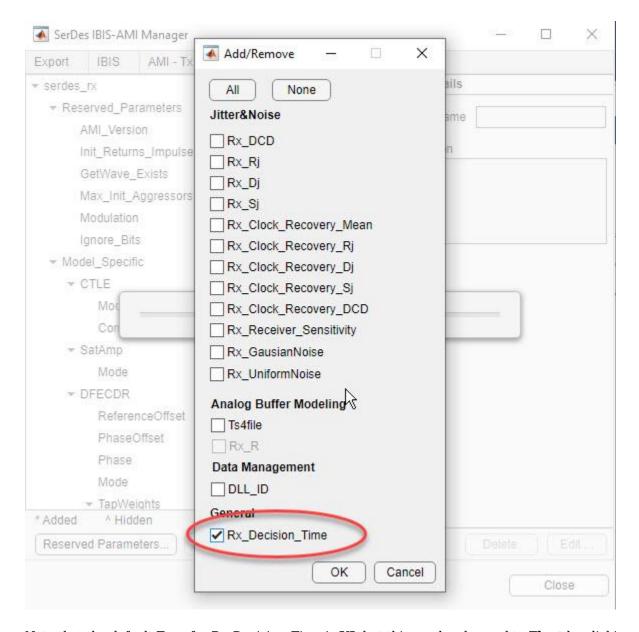

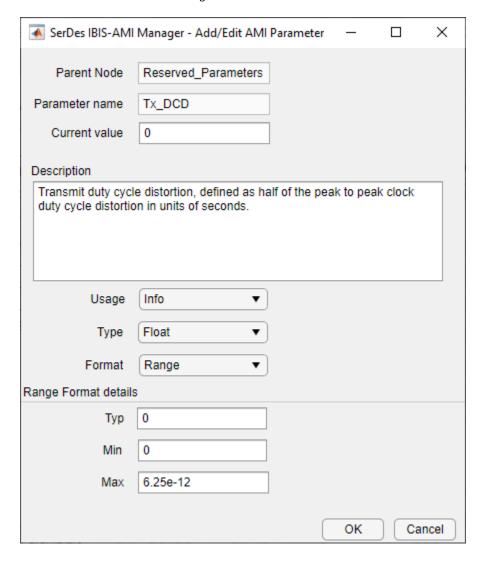

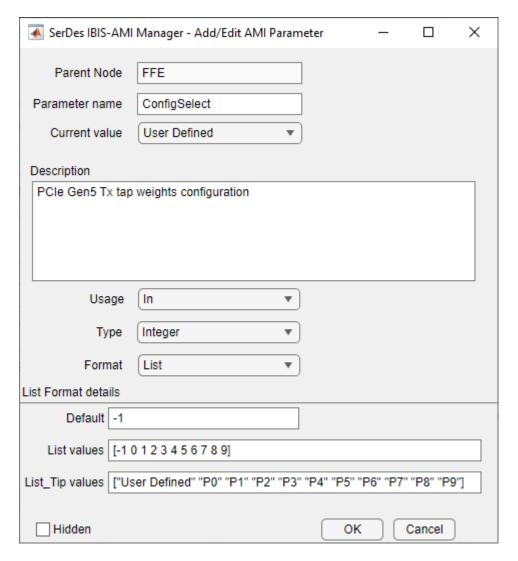

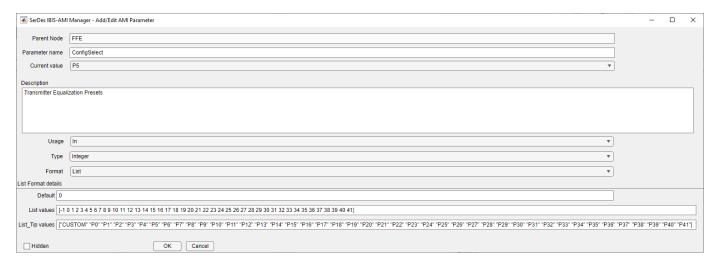

#### **Customize AMI Parameters**

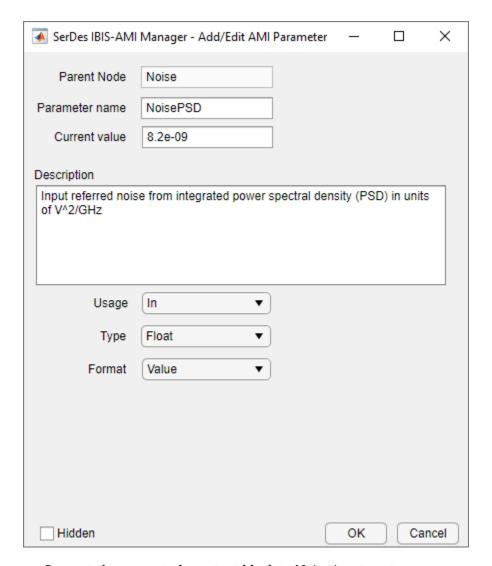

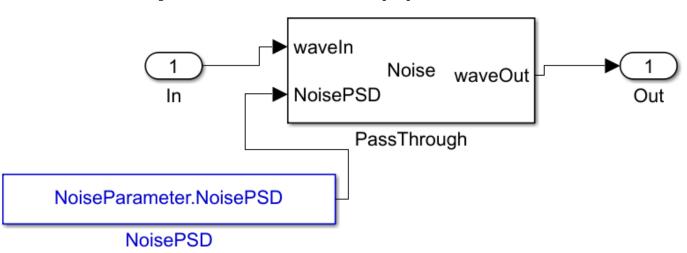

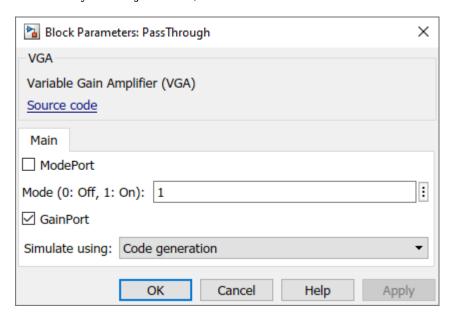

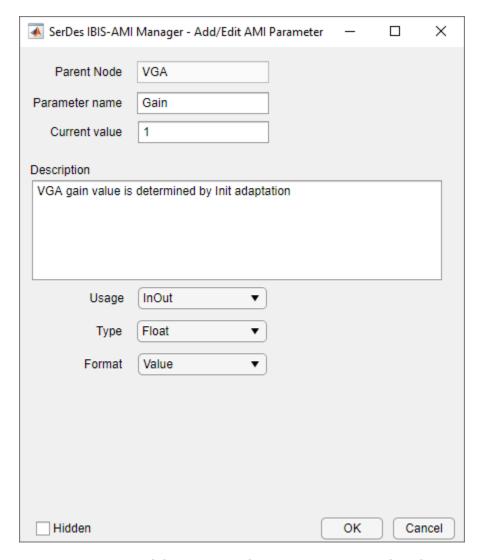

You can define and modify the parameters of individual transmitter and receiver blocks. From the Model\_Specific parameters, you can add new custom AMI parameters to specific blocks. The new AMI parameters references in the Simulink model are automatically maintained for you. For more information, see "Managing AMI Parameters" on page 6-2.

You can also add a new tap structure to the equalizer blocks. These additional taps are included both in the Simulink model and the exported IBIS-AMI models. The taps enable you to adjust equalization, especially when you build your custom blocks from scratch.

You can select to hide the Model\_Specific AMI parameters and tap structures using the Edit... button The parameters still work the same way in Simulink models. But they are not written in the AMI files and does not show up in the AMI\_Parameters\_Out string. The hidden parameters are hard-coded to their current values in the DLL files and the end user cannot modify them.

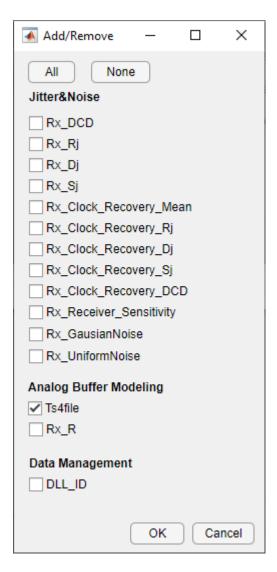

You can also include standard-compliant transmitter and receiver jitter and noise parameters to the Reserved\_Parameter section of the AMI file using the **Reserved Parameters...** button. Some of these reserved parameters are only used by the EDA tools. Simulink Coder™ ignores these parameters:

- Rx Decision Time

- Ts4file (and Tx V, Rx R)

- Rx Clock Recovery Mean

- Rx Clock Recovery Rj

- Rx\_Clock\_Recovery Dj

- Rx Clock Recovery Sj

- Rx Clock Recovery DCD

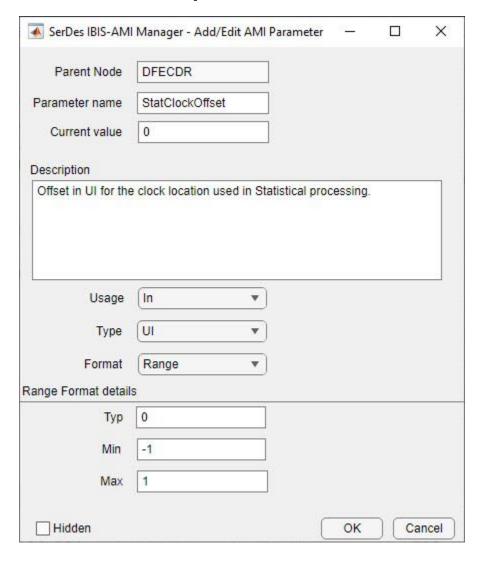

## **Define Clock Position in Statistical Eye**

You can define the timing of the clock in the statistical eye according to BIRD 205 using the reserved parameter Rx\_Decision\_Time. The corresponding Init function code, data structure, and AMI tree is automatically supported.

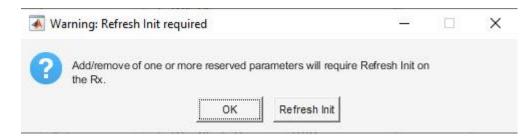

To add the Rx\_Decision\_Time parameter, click the **Reserved Parameters...** button in the AMI-Rx tab to open the Add/Remove dialog box. Once you add the parameter, it appears in the AMI tree. A

model workspace variable is also created You need to refresh the Init function in the receiver after you modify the Rx Decision Time parameter. After refreshing the Init function, the parameter appears in the Custom User Area.

You can use a CDR or DFECDR with baud-rate type-A phase detector model in the **SerDes Designer** app and then export the model to Simulink. In this case, automatically adds the Rx Decision Time parameter to define the clock position. If you want to change the phase detector model in Simulink, you need to manually add the Rx Decision Time parameter.

**Note** The Rx Decision Time parameter is only added in the receiver section.

## **PAMn Capabilities**

The SerDes IBIS-AMI manager supports NRZ, PAM3, PAM4, PAM8, and PAM16 modulation schemes. If your model previously was created using IBIS pre-7.2 modulation levels, you can switch to IBIS 7.2 parameter Modulation Levels by editing the Modulation AMI parameter under the Reserved Parameter section. Switching to IBIS 7.2 parameter Modulation Levels requires refreshing the Init function in the receiver side. The changes are applied both to transmitter and the receiver side.

## **Debug AMI Files in EDA**

To enable debugging the AMI files in EDA tools, in the AMI-Tx or AMI-Rx tab, click the Reserved Parameters... button and select DLL ID parameter. DLL ID is a standard IBIS-AMI parameter that appears as a Reserved Parameter. It also enables the AMI Debug parameter as a Model Specific parameter.

Set **Enable** value to true to output debug files. You can improve performance by setting **Enable** value to false and not output any debug files, but still have the option to turn on debugging in the EDA tools if necessary. Use **Start Time** to define the simulation time at which debug output generation begins.

**Note** SerDes Toolbox does not support compilation of AMI Wrapper.cpp files with non-inlined Sfunctions. As a result, you cannot export IBIS-AMI models with non-inlined S-functions. If you have a Simulink Coder or Embedded Coder® license, you can convert your S-functions to inlined to support IBIS-AMI model export. For more information, see "Inlining S-Functions" (Simulink Coder).

#### See Also

Configuration

#### More About

"Managing AMI Parameters" on page 6-2

#### **External Websites**

https://ibis.org

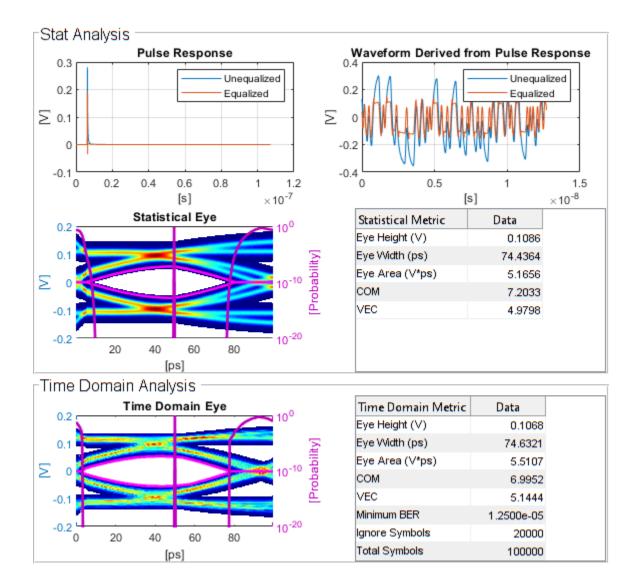

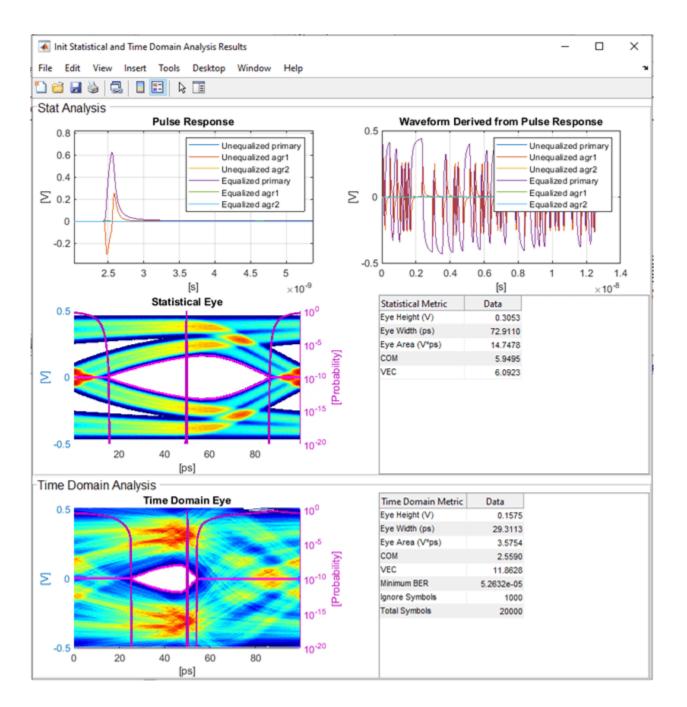

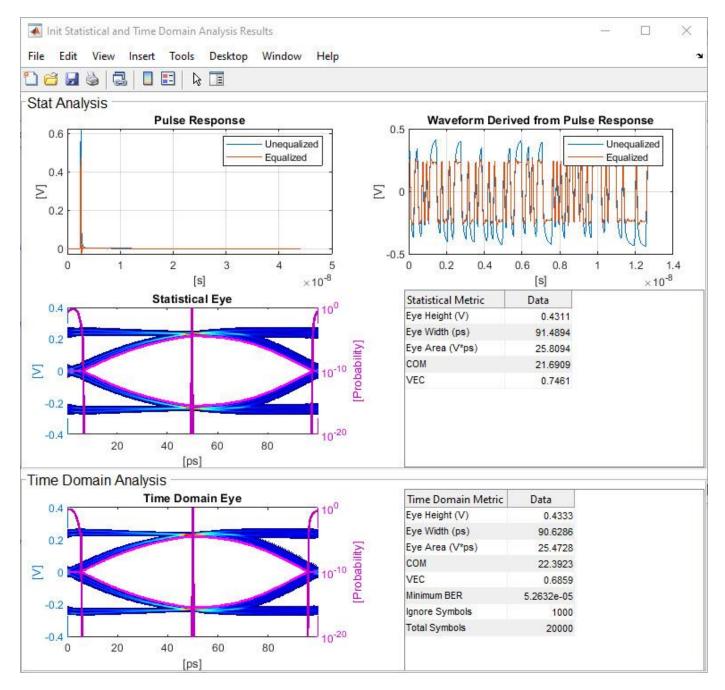

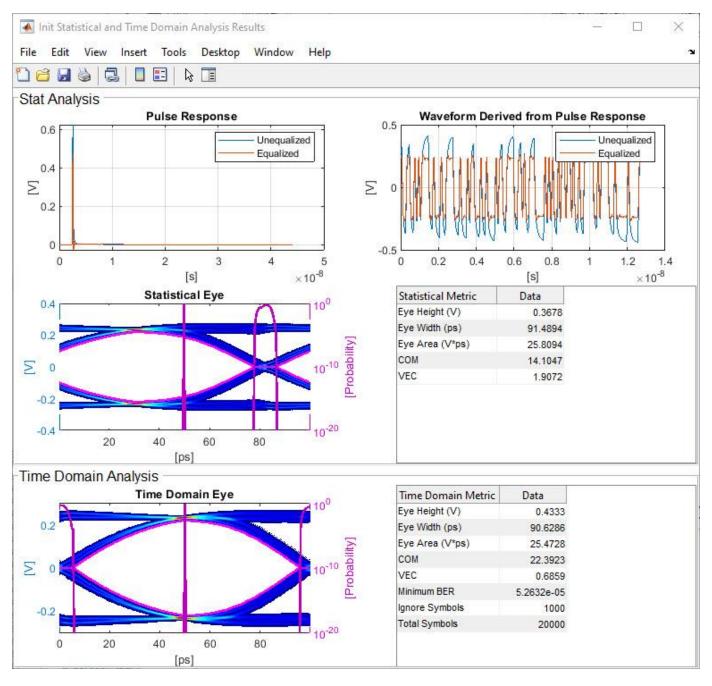

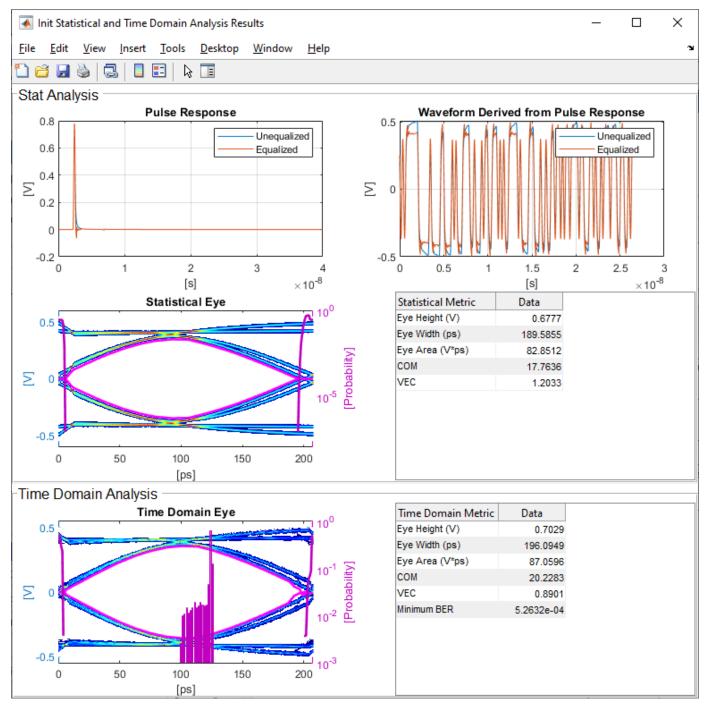

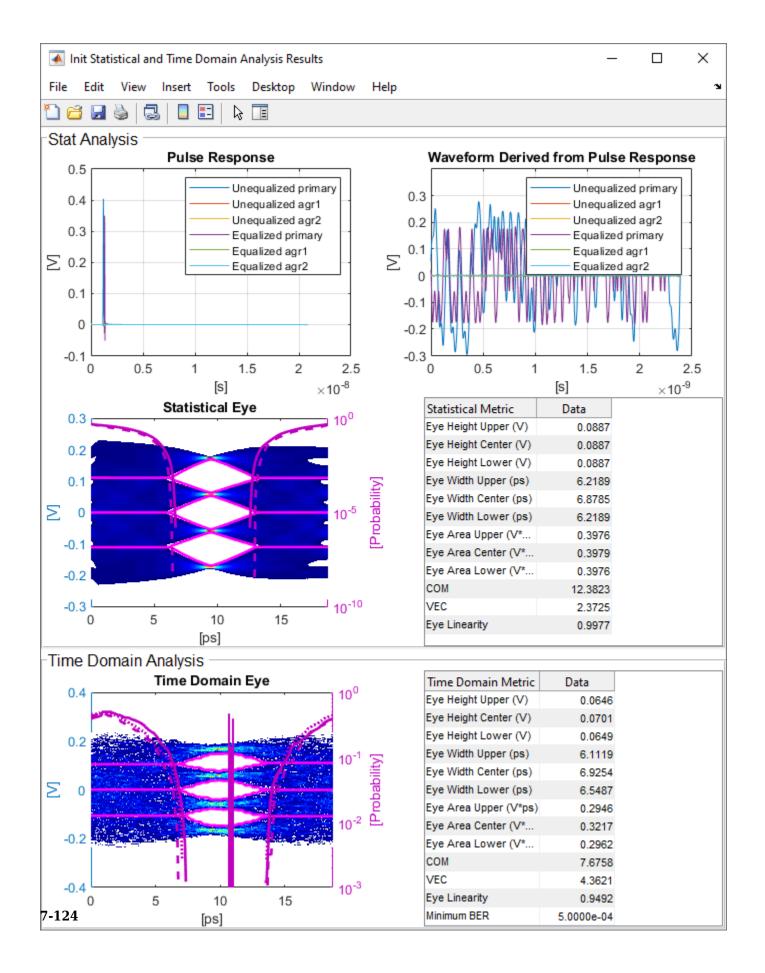

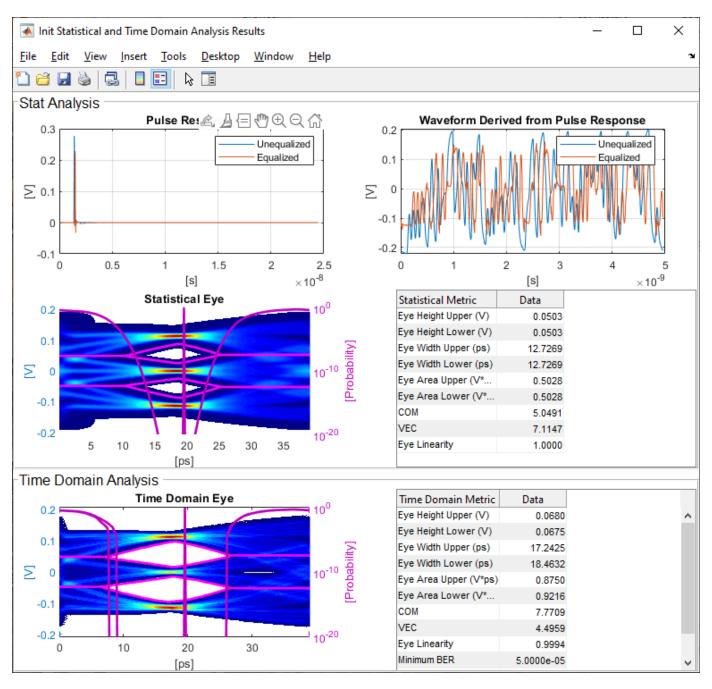

## Statistical Analysis in SerDes Systems

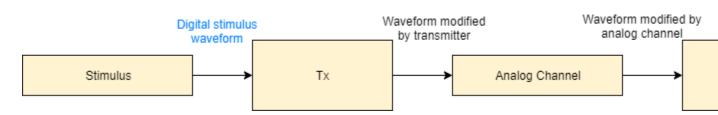

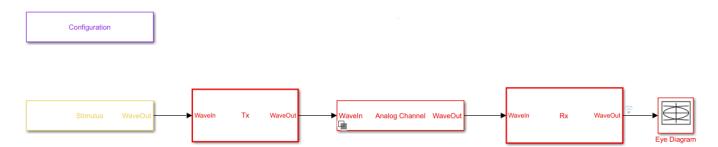

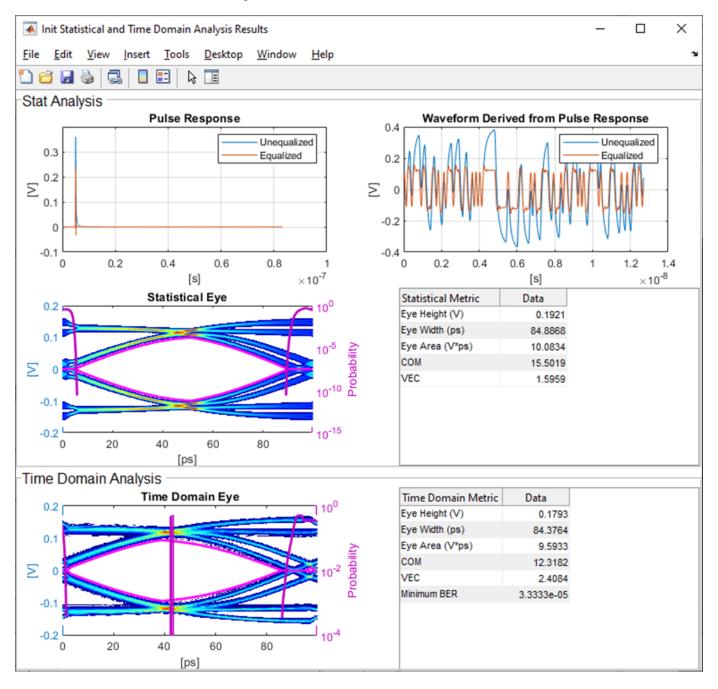

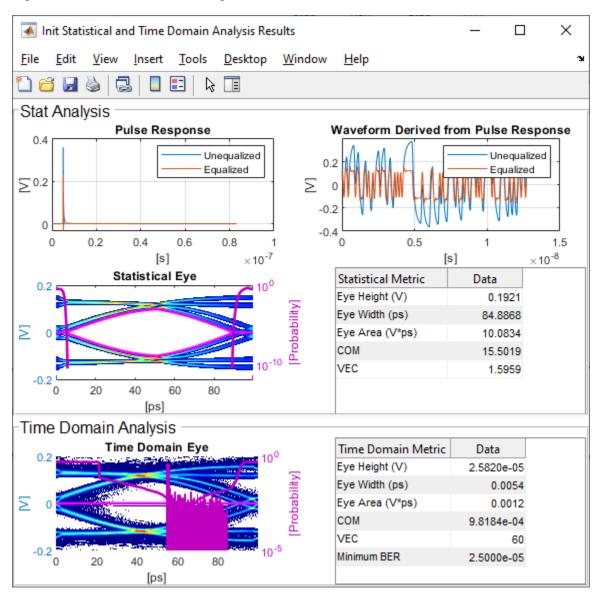

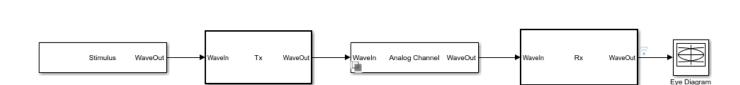

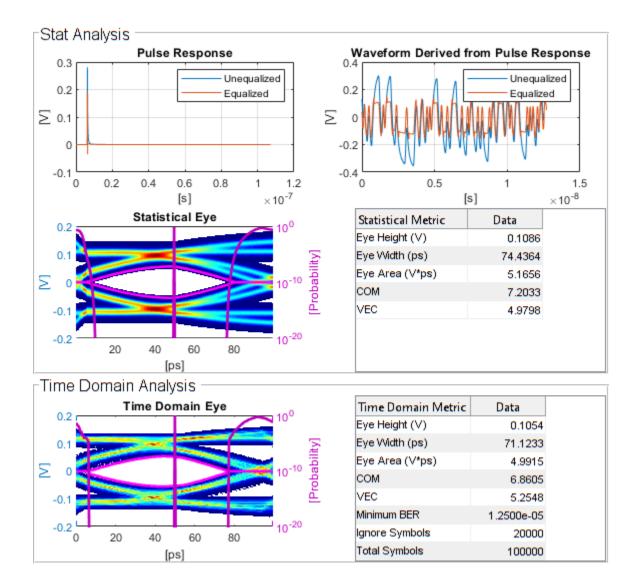

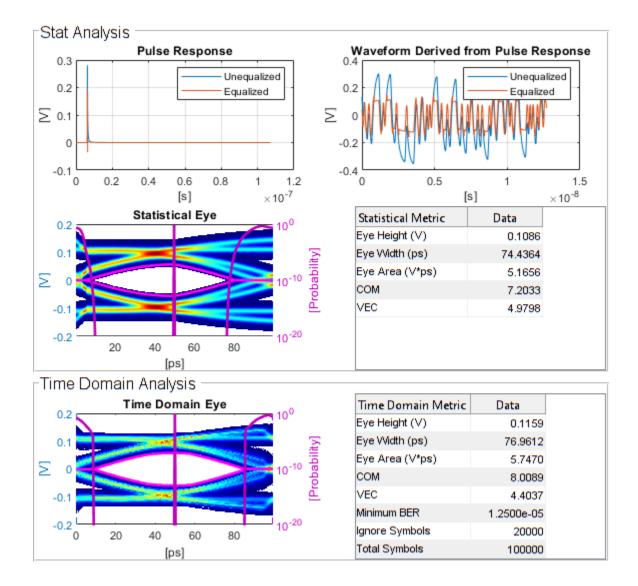

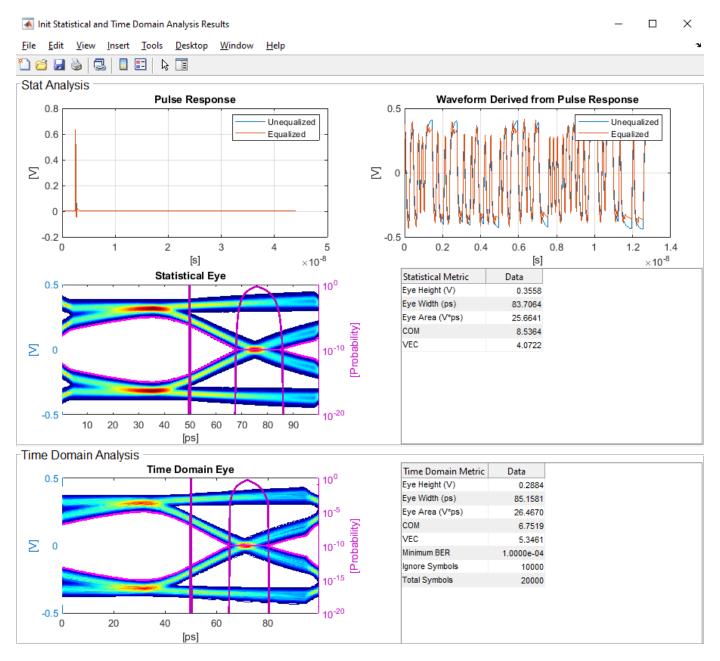

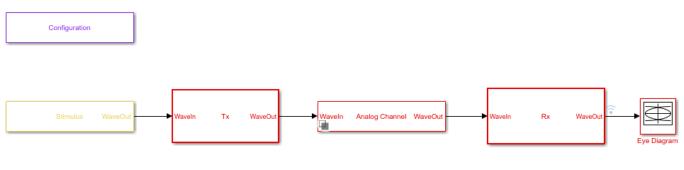

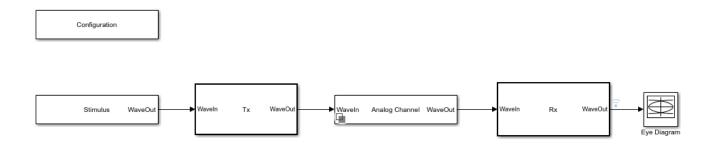

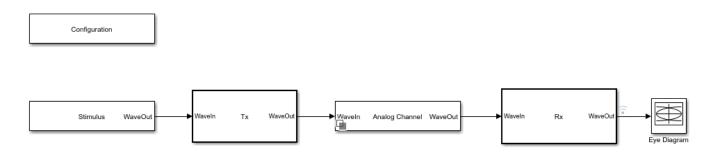

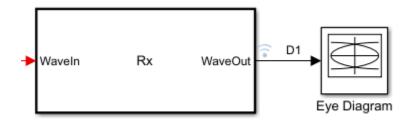

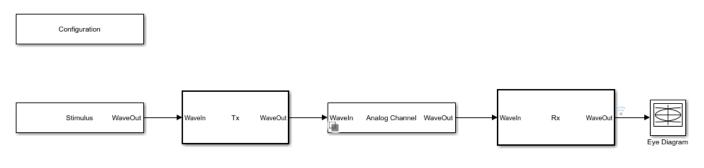

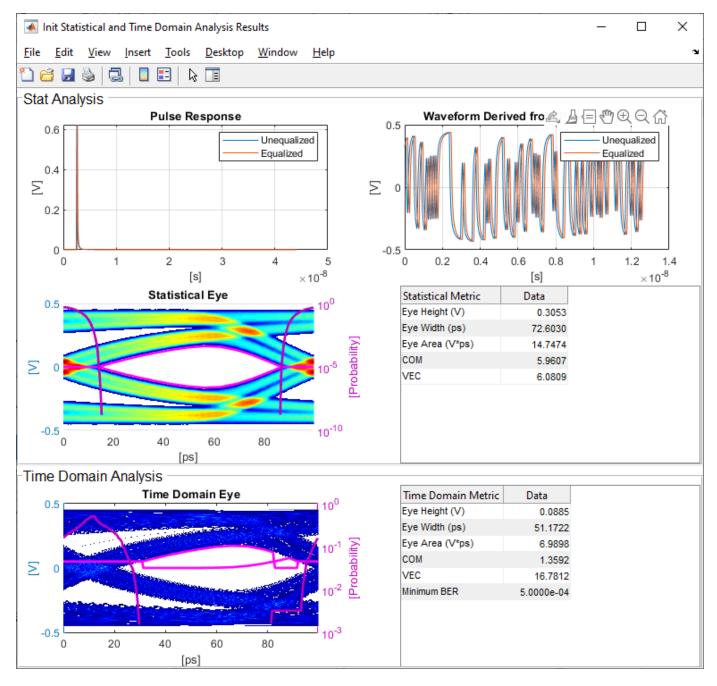

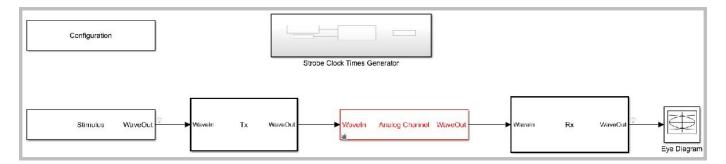

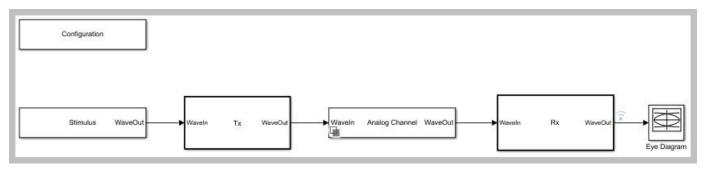

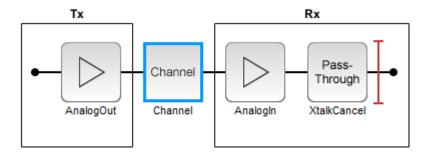

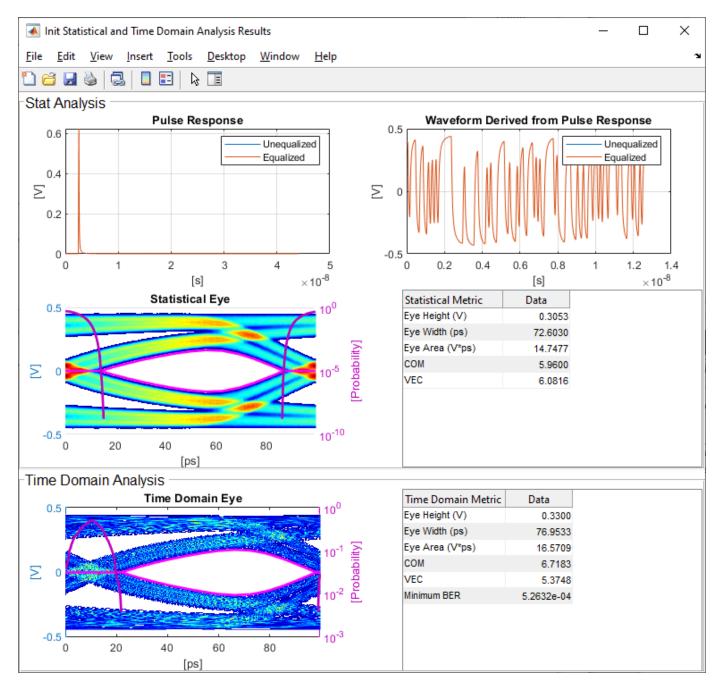

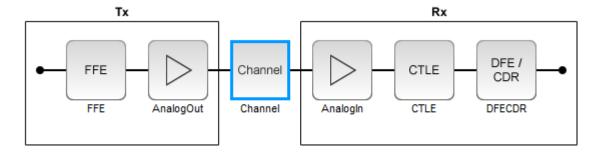

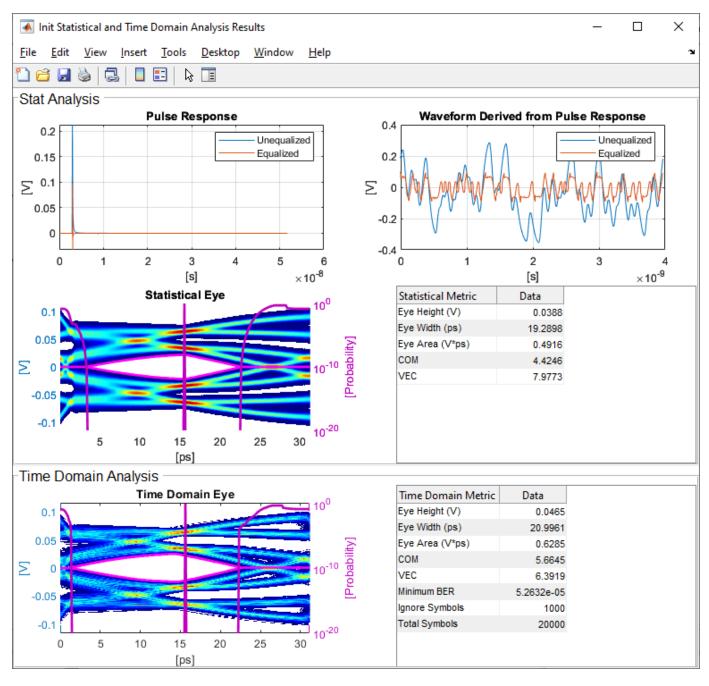

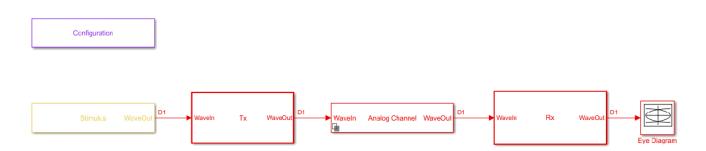

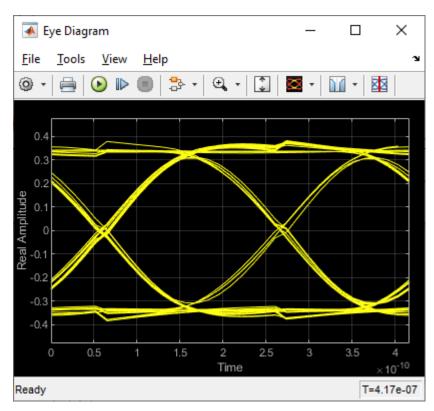

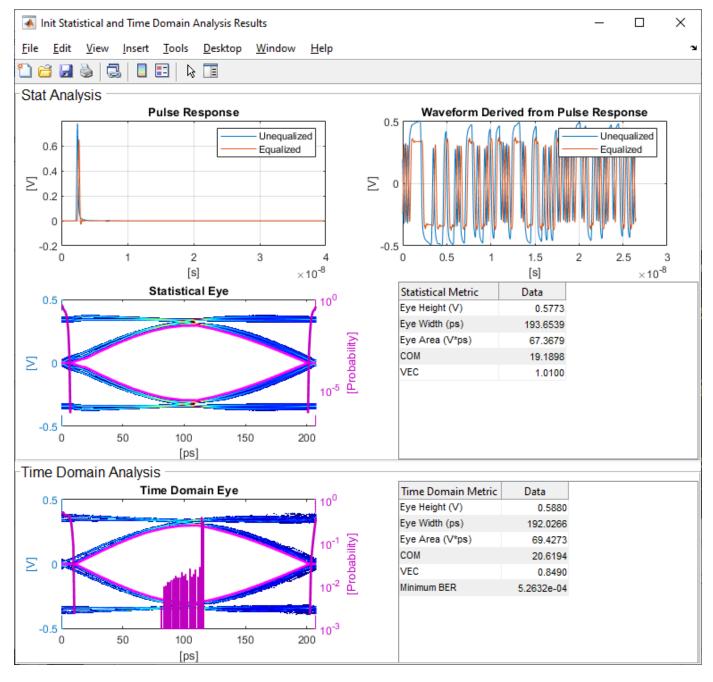

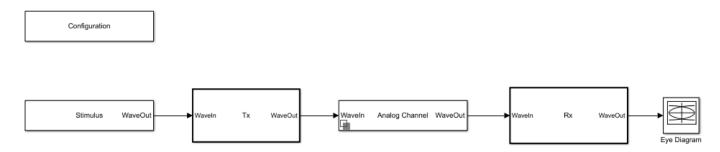

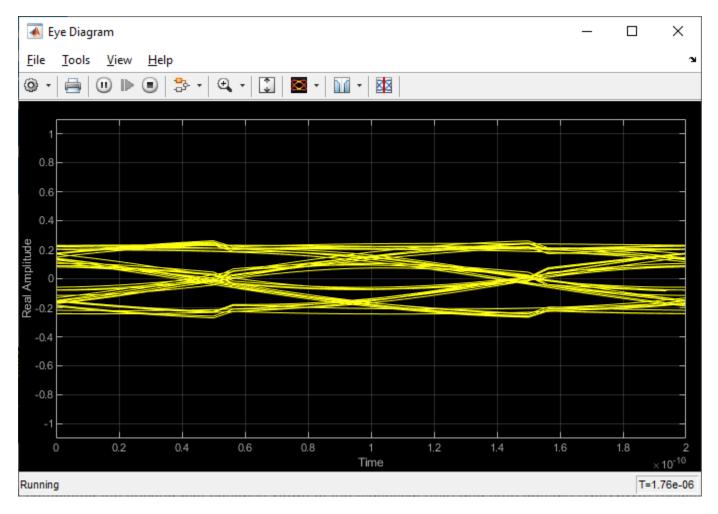

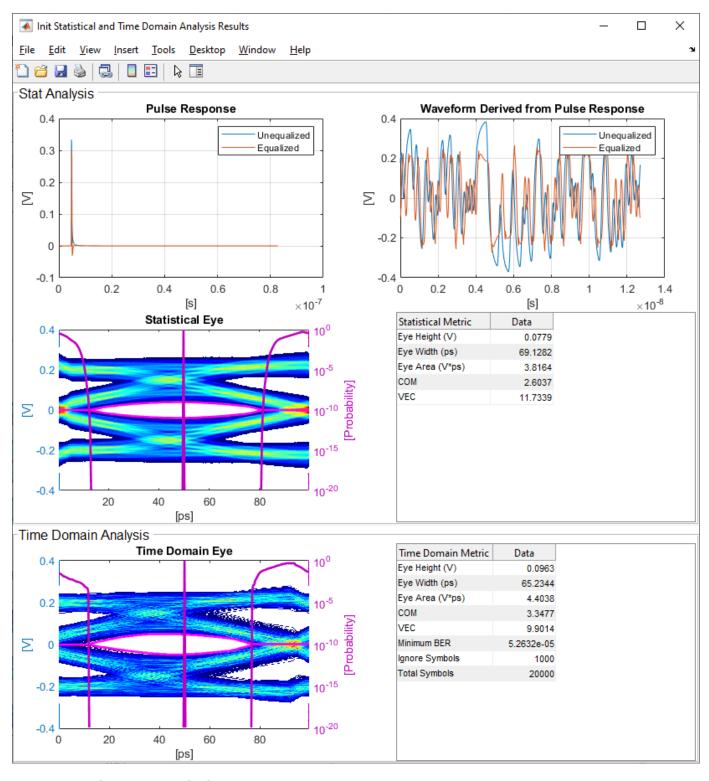

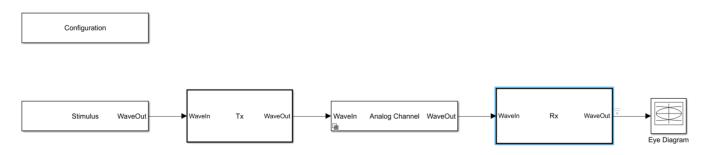

A SerDes system simulation involves a transmitter (Tx) and a receiver (Rx) connected by a passive analog channel. There are two distinct phases to a SerDes system simulation: statistical analysis and time-domain analysis. Statistical analysis (also known as analytical, linear time-invariant, or Init analysis) is based on impulse responses enabling fast analysis and adaptation of equalization algorithms. Time-domain analysis (also known as empirical, bit-by-bit or GetWave analysis) is a waveform-based implementation of equalization algorithms that can optionally include nonlinear effects.

The reference flow of statistical analysis differs from time-domain analysis. During a statistical analysis simulation, an impulse response is generated. The impulse response represents the combined response of the transmitter's analog output, the channel, and the receiver's analog front end. The impulse response of the channel is modified by the transmitter model's statistical functions. The modified impulse response from the transmitter output is then further modified by the receiver model's statistical functions. The simulation is then completed using the final modified impulse response which represents the behavior of both AMI models combined with the analog channel.

During a time-domain simulation, a digital stimulus waveform is passed to the transmitter model's time-domain function. This modified time-domain waveform is then convolved with the analog channel impulse response used in the statistical simulation. The output of this convolution is then passed to the receiver model's time-domain function. The modified output of the receiver becomes the simulation waveform at the receiver latch.

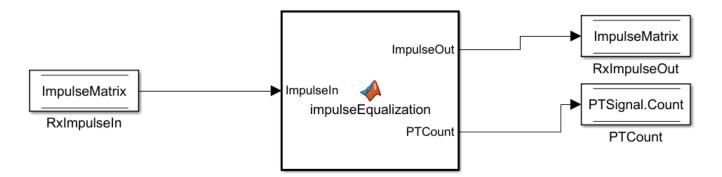

In SerDes Toolbox, the Init subsystem within both the Tx and Rx blocks uses an Initialize Function Simulink block. The Initialize Function block contains a MATLAB® function to handle the statistical analysis of an impulse response vector. The impulse response vector is generated by the Analog Channel block.

The MATLAB code within the Init subsystems mimics the architecture of Simulink time-domain simulation by initializing and setting up the library blocks from the SerDes Toolbox that implement equalization algorithms. Each subsystem then processes the impulse response vector through one or more System objects representing the corresponding blocks.

Additionally, an Init subsystem can adapt or optimize the equalization algorithms and then apply the modified algorithms to the impulse response. The output of an Init subsystem is an adapted impulse response. If the Init subsystem adapts the equalization algorithms, it can also output the modified equalization settings as AMI parameters. These modified equalization parameters can also be passed to the time-domain analysis as an optimal setting or to provide a starting point for faster time-domain adaptation.

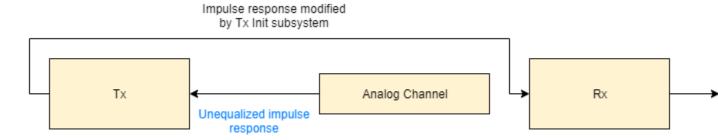

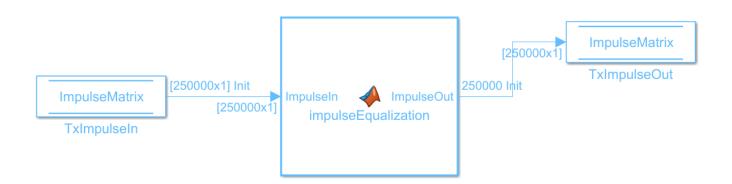

## **Init Subsystem Workflow**

In a Simulink model of a SerDes system, there are two Init subsystems, one on the transmitter side (Tx block) and one on the receiver side (Rx block). During statistical analysis, the impulse response of the analog channel is first equalized by the Init subsystem inside the Tx block based on the System object properties. The modified impulse response is then fed as an input to the Rx block. The Init system inside the Rx block further equalizes the impulse response and produces the final output.

The System objects corresponding to the Tx and Rx blocks modify the impulse response in the same order as they were received. If there are multiple self-adapting System objects in a Tx or Rx block, each System object finds the best setting for the impulse response and modifies it before sending it to the next System object.

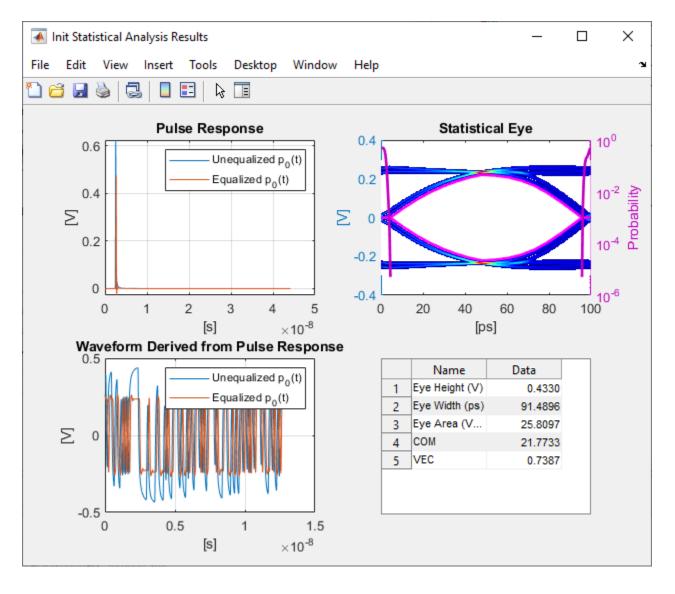

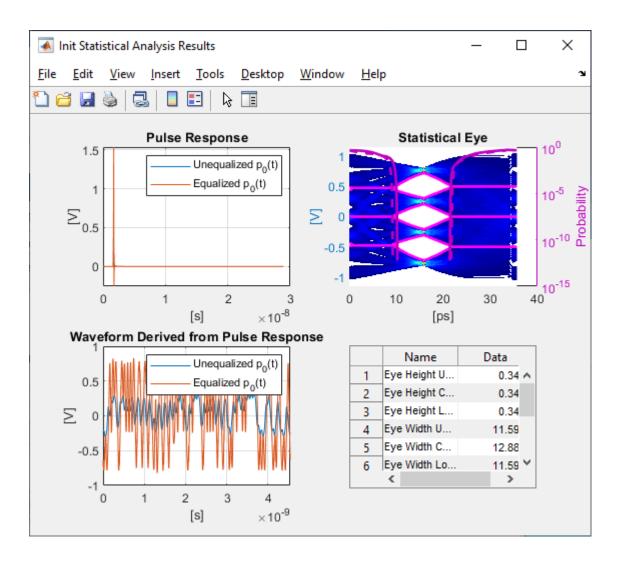

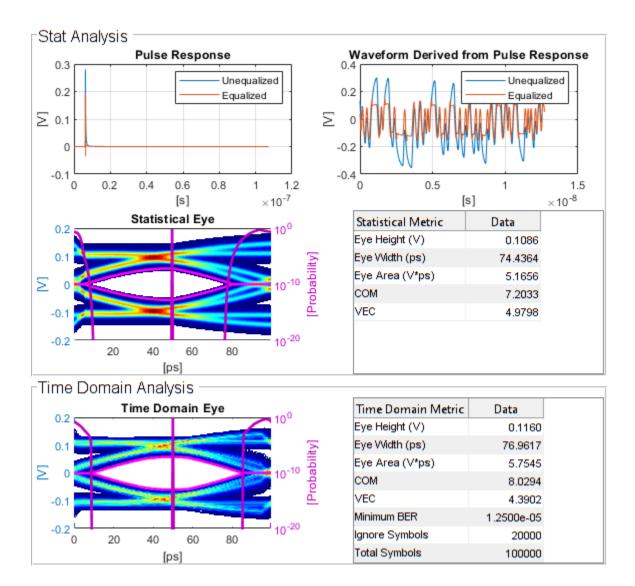

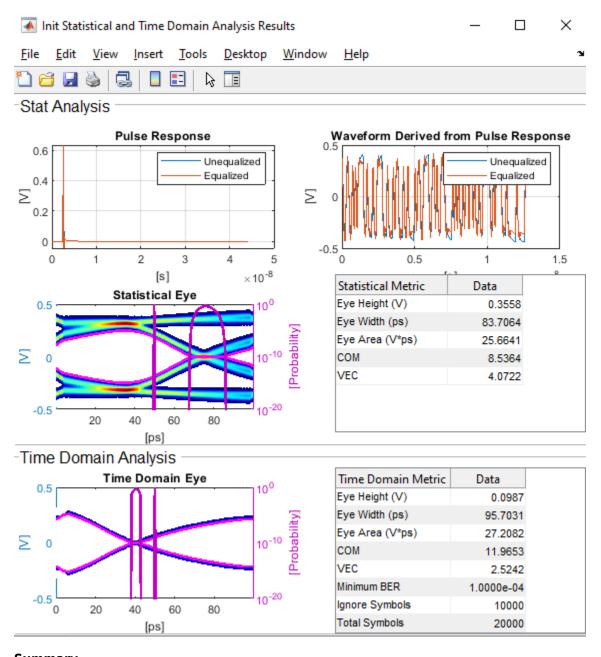

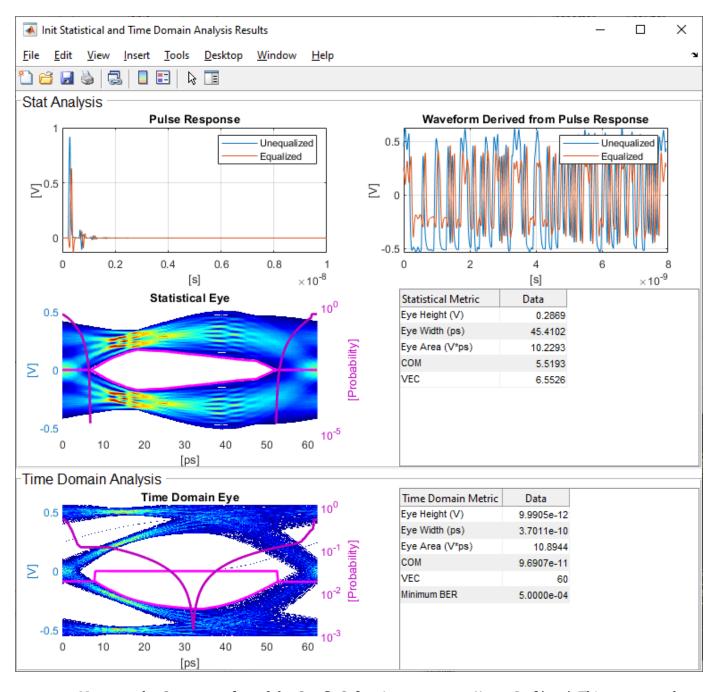

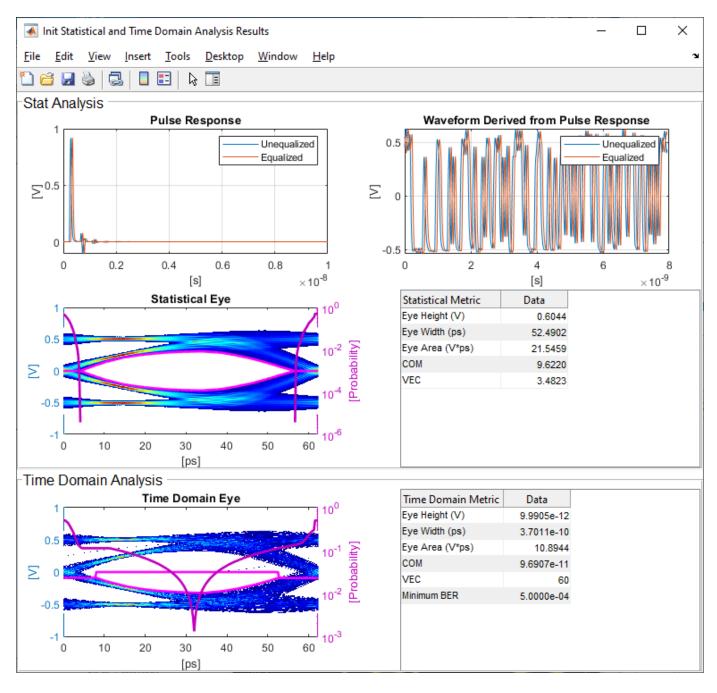

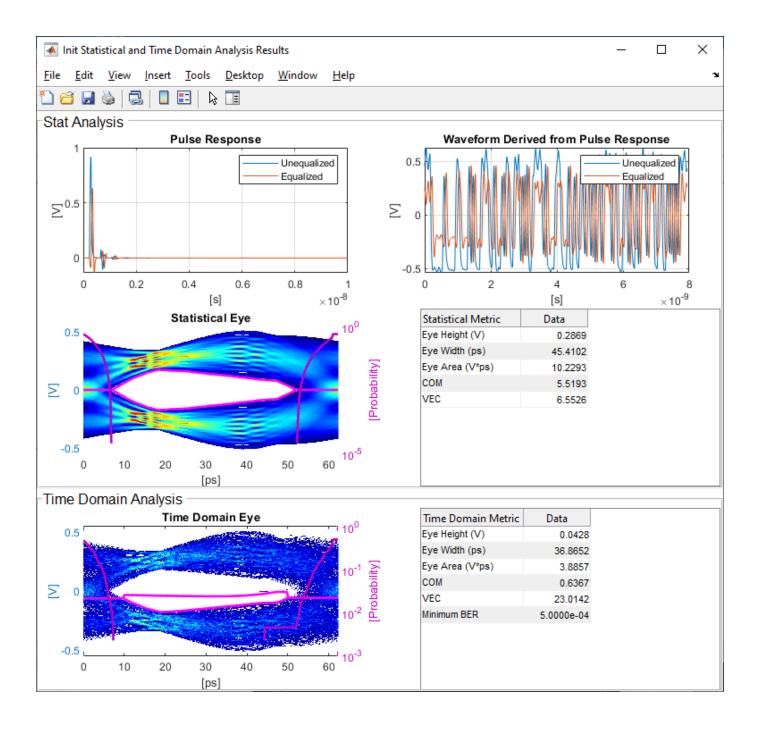

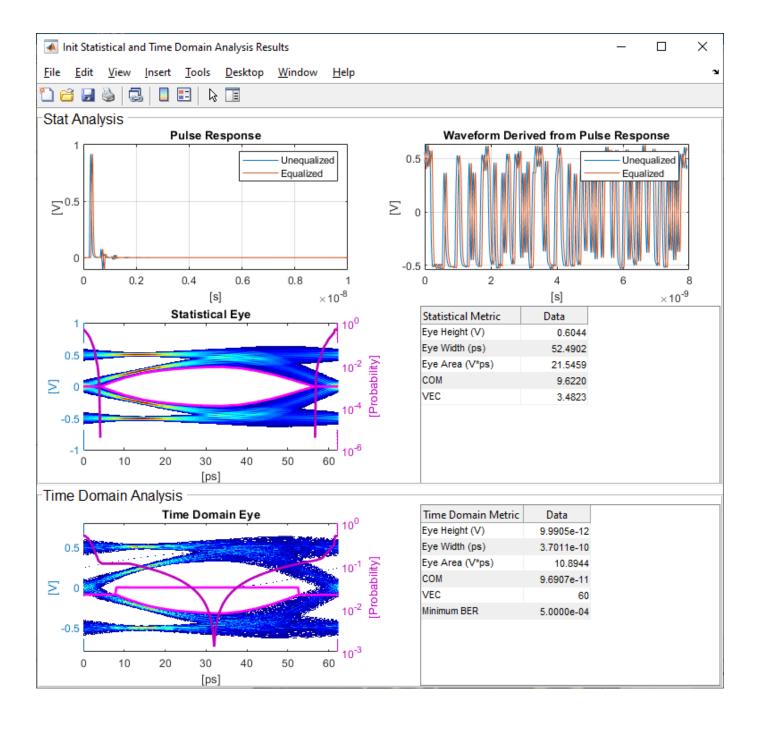

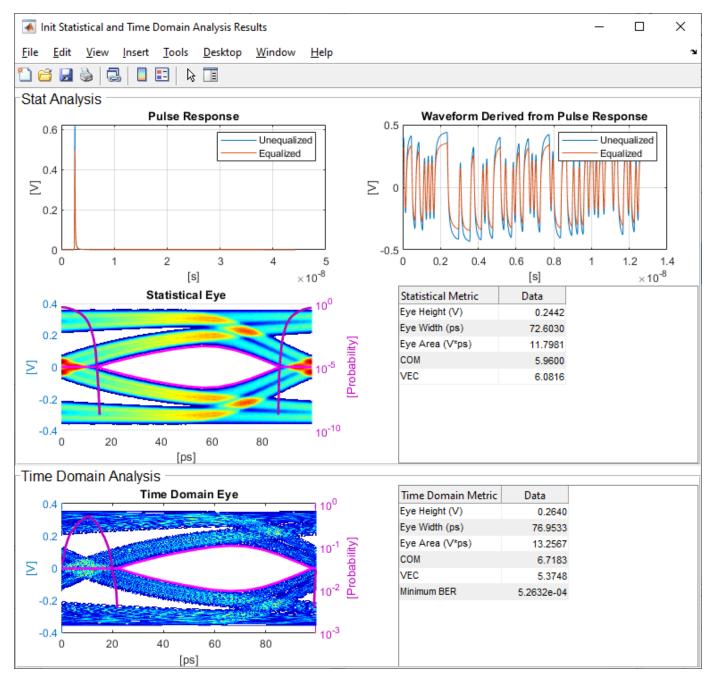

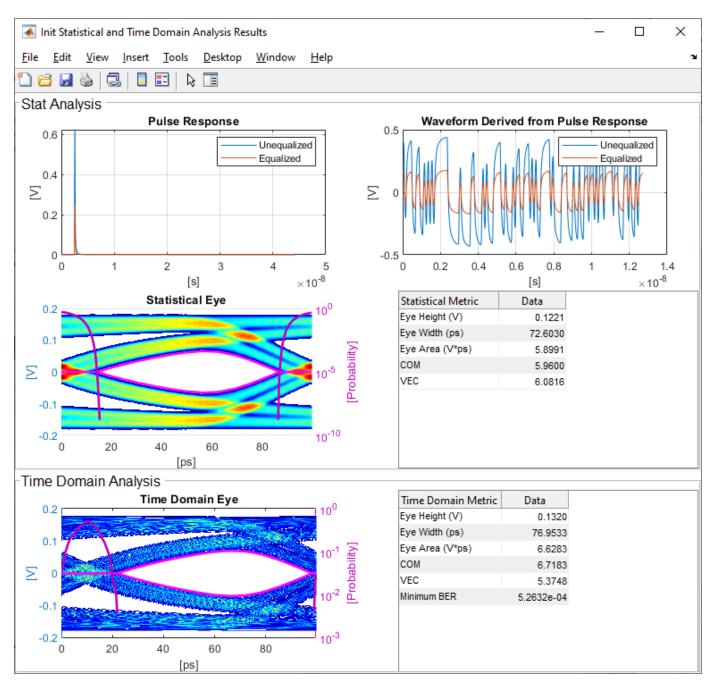

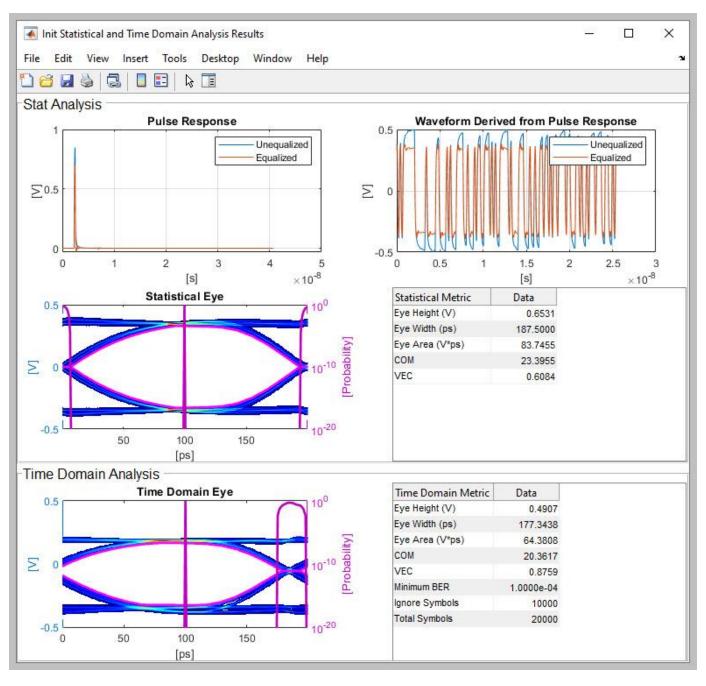

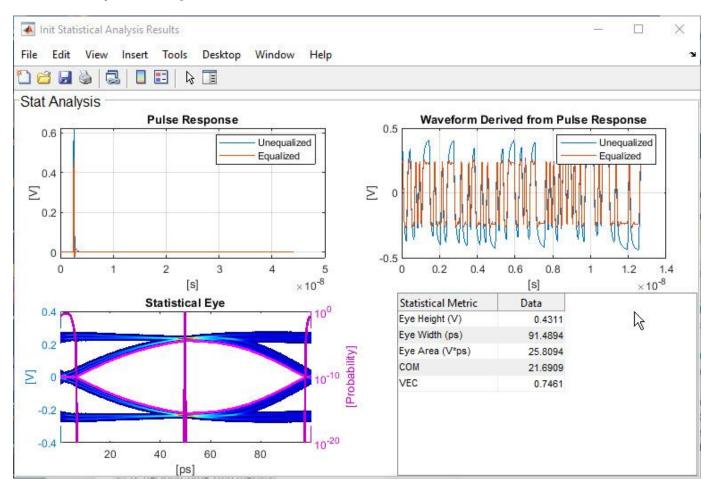

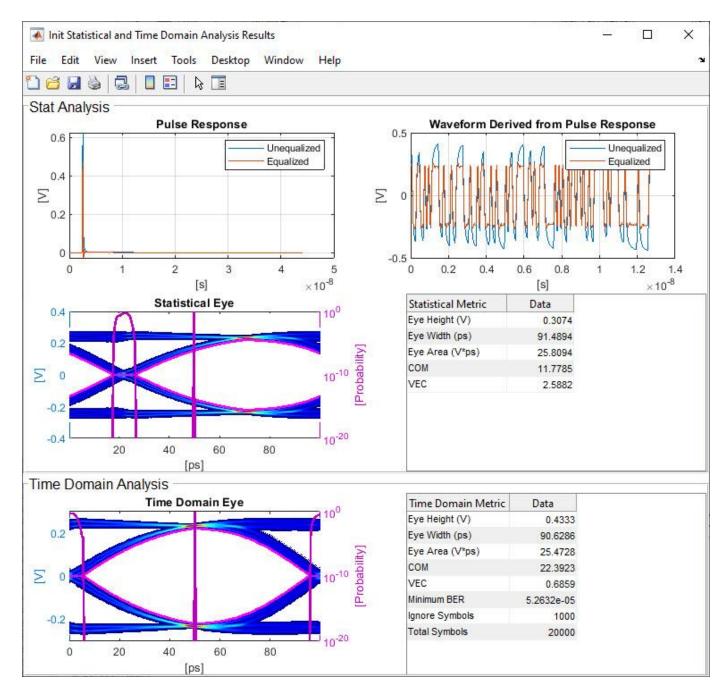

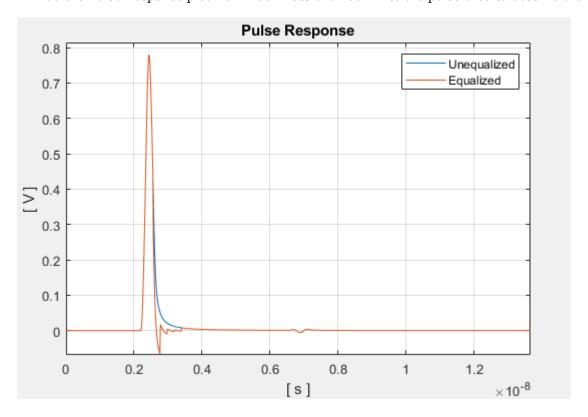

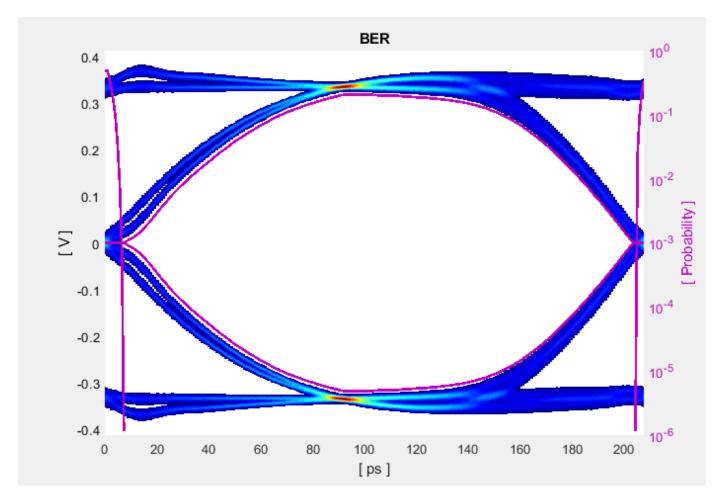

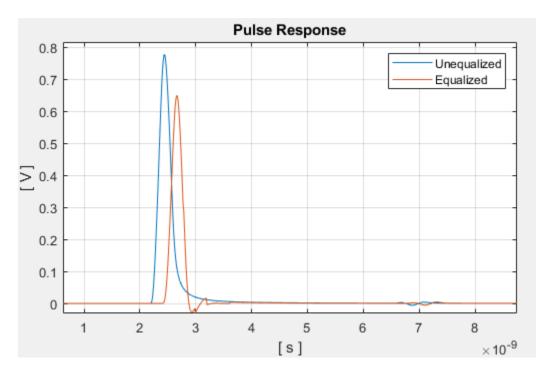

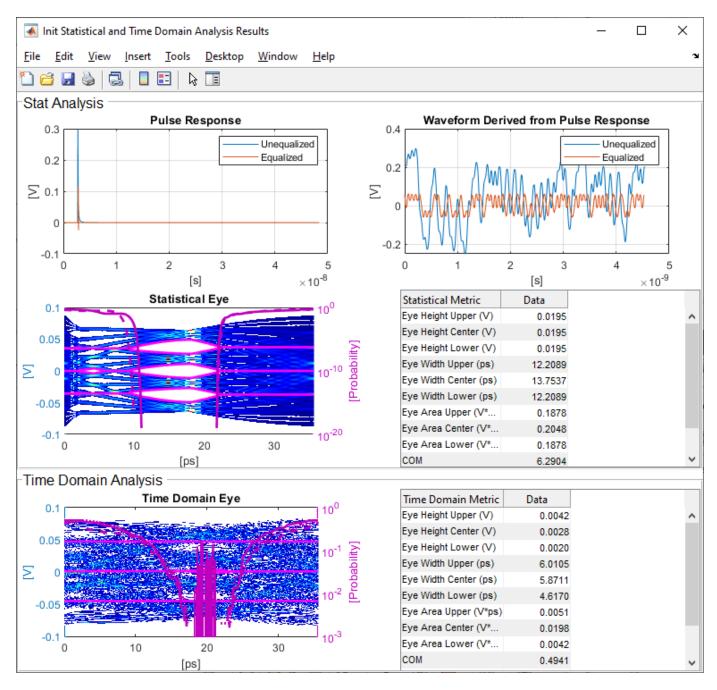

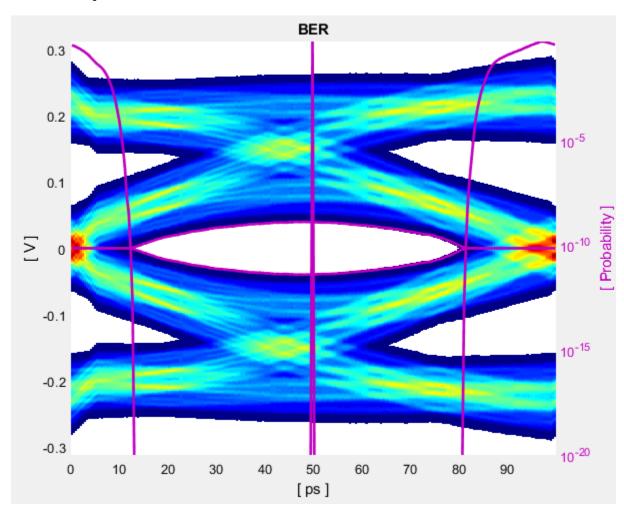

The final equalized impulse response is used to derive the pulse response, statistical eye, and the waveforms.

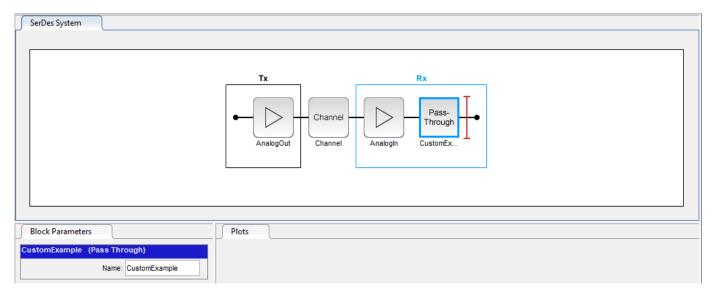

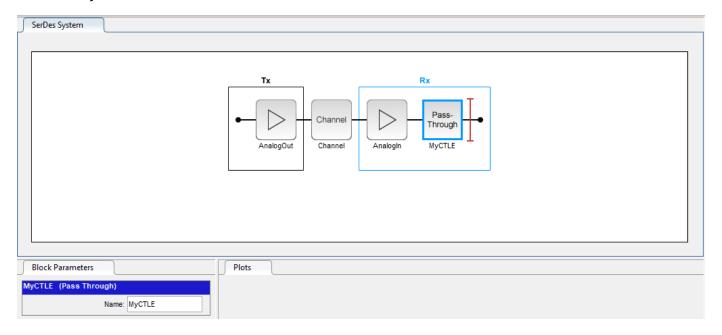

## **SerDes System Using Init Subsystem**

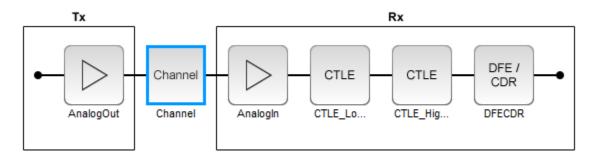

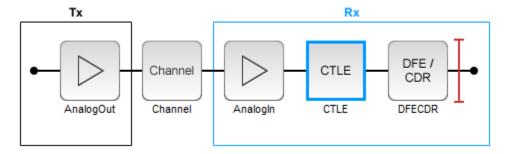

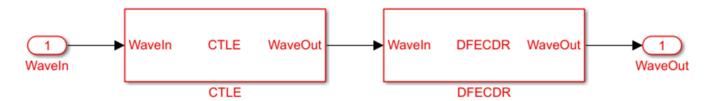

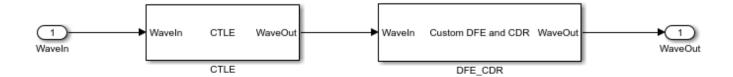

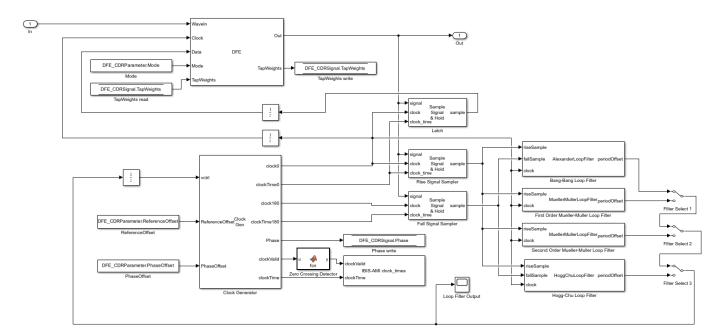

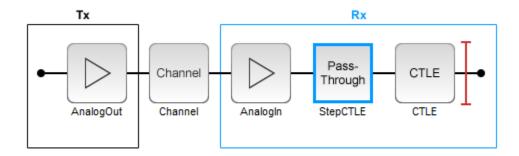

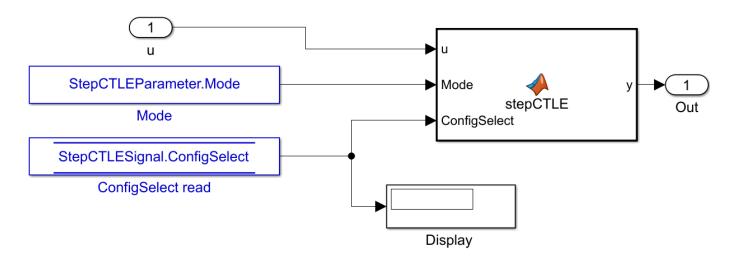

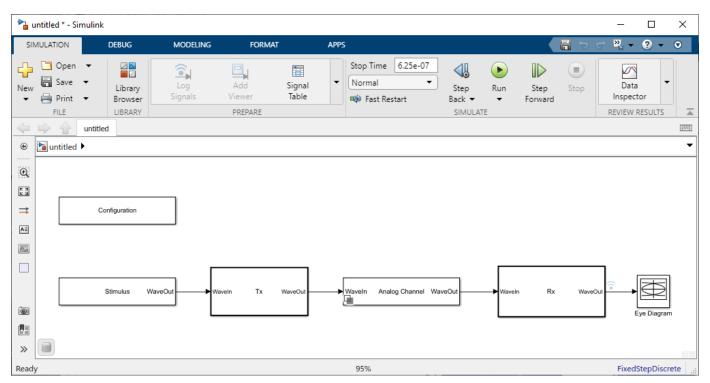

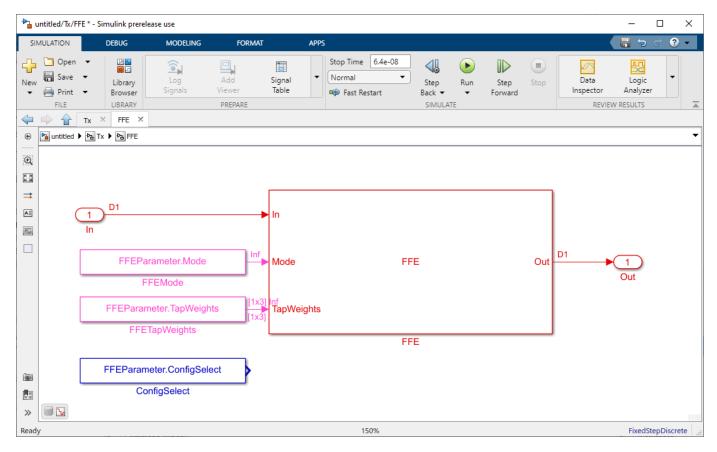

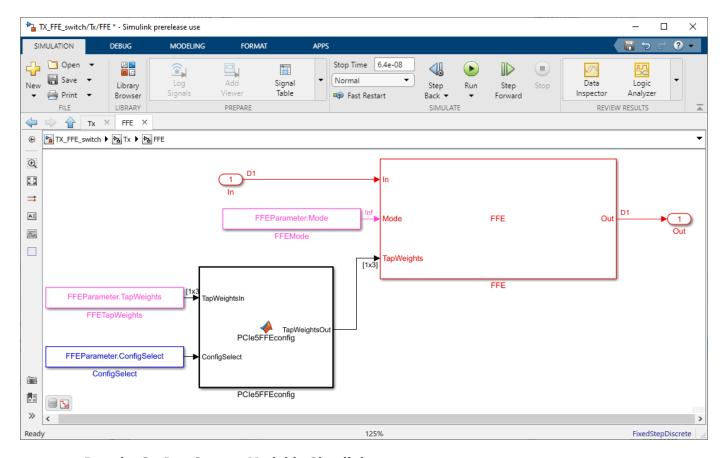

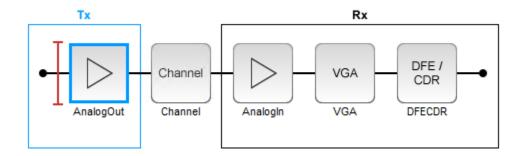

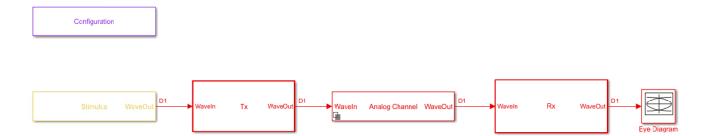

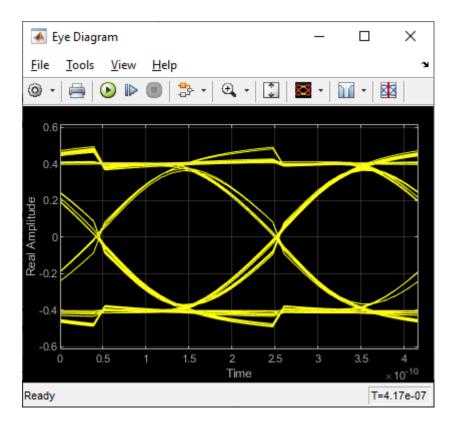

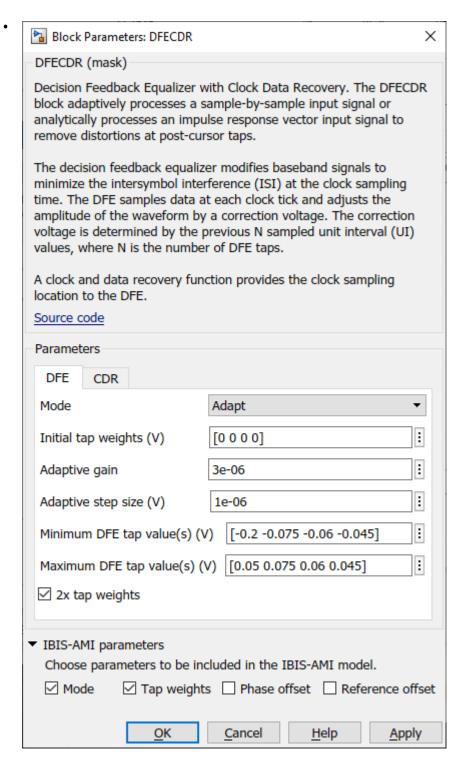

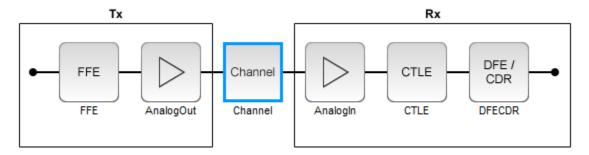

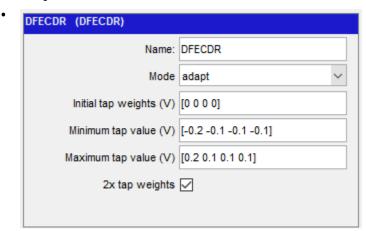

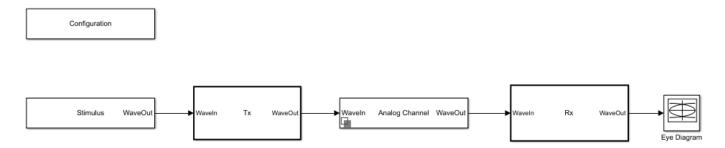

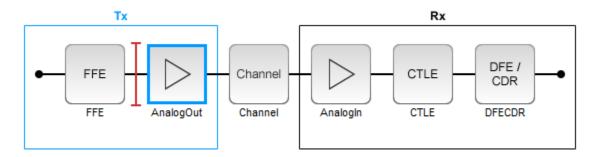

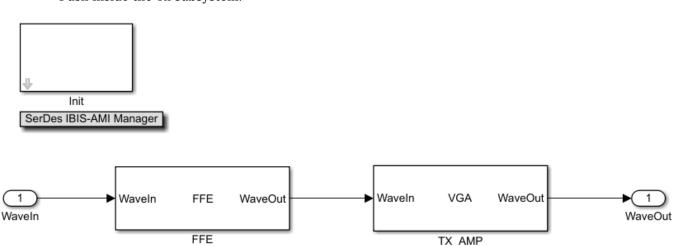

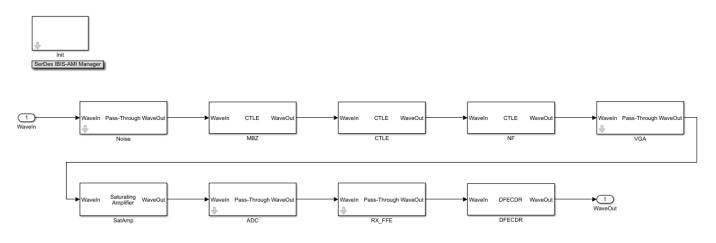

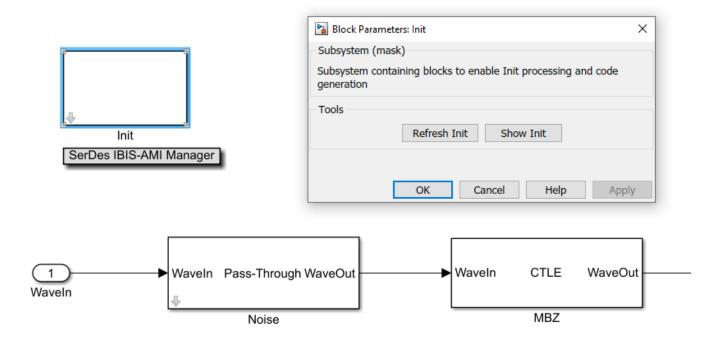

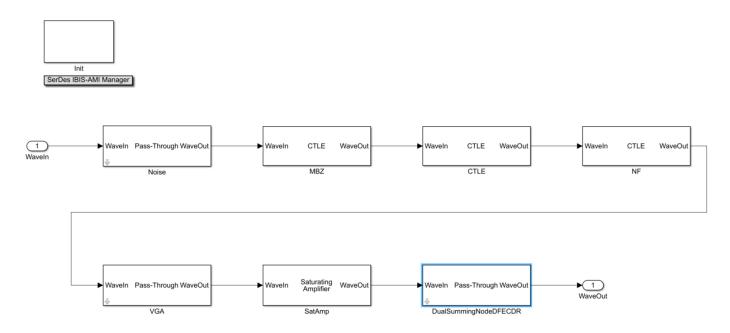

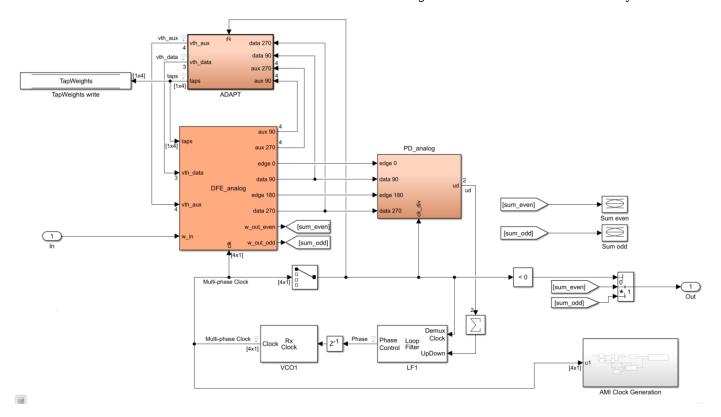

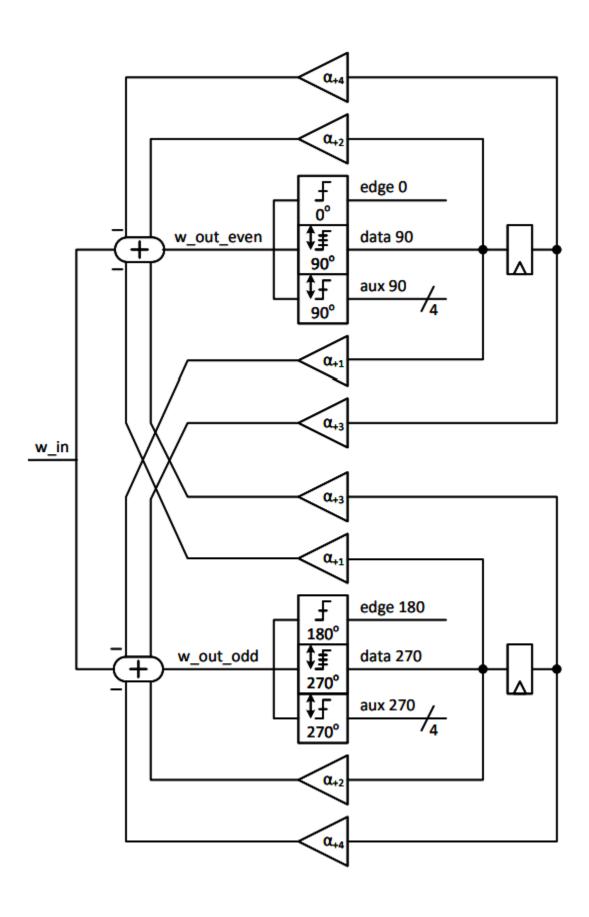

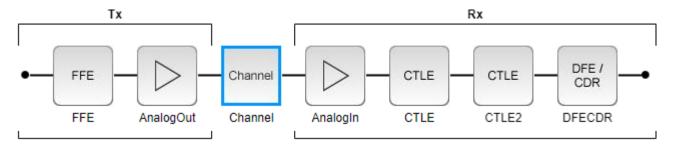

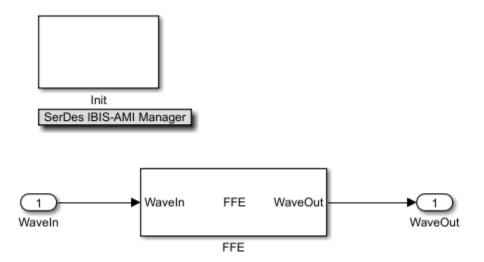

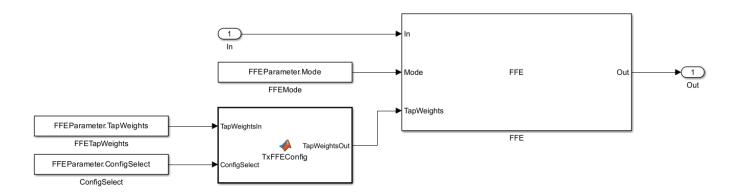

To understand how an Init subsystem handles statistical analysis in a SerDes system, create a SerDes system using the **SerDes Designer** app. The SerDes system contains an FFE block on the Tx side and CTLE and DFECDR blocks on the Rx side. Use the default settings for each block.

#### **Access Init Code**

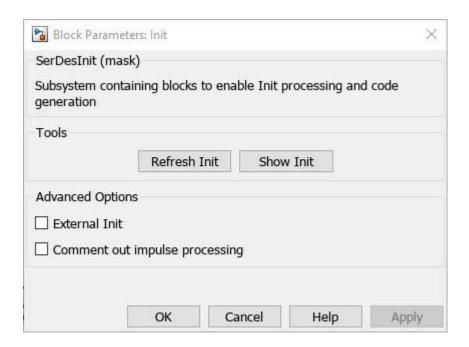

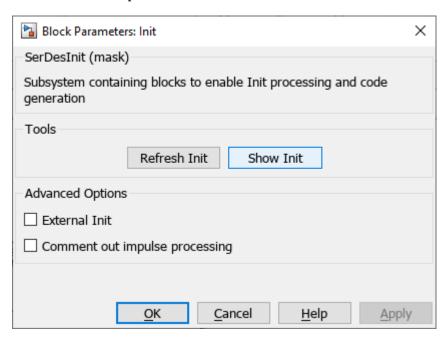

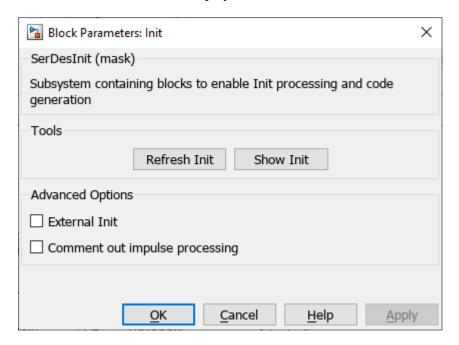

Export the SerDes system to a Simulink model. In Simulink, double-click the Tx block to open the Init block. Then double-click the Init block to open the Block Parameters dialog box. Click the **Show Init** button to open the code pertaining to the Init function of the transmitter.

#### Reshape Impulse Response and Instantiate Tx System object

The Init function first reshapes the impulse response vector of the analog channel into a 2-D matrix. The first column in the 2-D matrix represents the analog channel impulse response (victim). The subsequent columns (if any are present) represent the crosstalk (aggressors).

```

% Impulse response formatting

% Size ImpulseOut by setting it equal to ImpulseIn

ImpulseOut = ImpulseIn;

% Reshape ImpulseIn vector into a 2D matrix using RowSize and Aggressors called LocalImpulse

LocalImpulse = zeros(RowSize,Aggressors+1);

AggressorPosition = 1;

for RowPosition = 1:RowSize:RowSize*(Aggressors+1)

LocalImpulse(:,AggressorPosition) = ImpulseIn(RowPosition:RowSize-1+RowPosition)';

AggressorPosition = AggressorPosition+1;

end

```

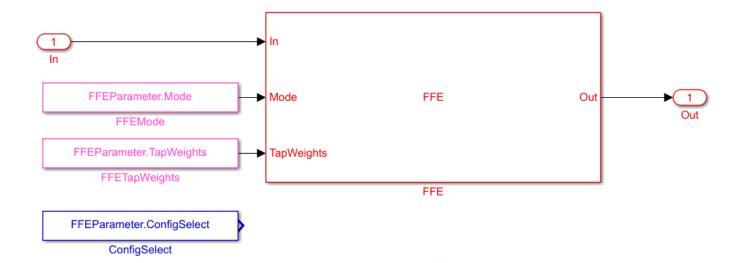

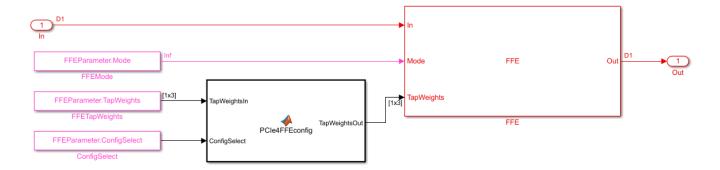

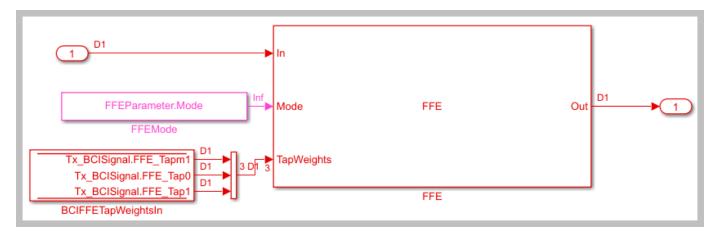

Then the Init function initializes the system objects that represent the blocks on the Tx side and sets up the simulation and AMI parameters and the block properties. In this SerDes system, there is only one block on the Tx side. FFE.

```

% Instantiate and setup system objects

% Create instance of serdes.FFE for FFE

FFEInit = serdes.FFE('WaveType', 'Impulse');

% Setup simulation parameters

FFEInit.SymbolTime = SymbolTime;

FFEInit.SampleInterval = SampleInterval;

% Setup FFE In and InOut AMI parameters

FFEInit.Mode = FFEParameter.Mode;

FFEInit.TapWeights = FFEParameter.TapWeights;

% Setup FFE block properties

FFEInit.Normalize = true;

```

#### Tx Impulse Response Processing

The channel impulse response is then processed by the System object on the Tx side.

```

%% Impulse response processing via system objects

% Return impulse response for serdes.FFE instance

LocalImpulse = FFEInit(LocalImpulse);

```

The modified impulse response in 2-D matrix form is reshaped back into an impulse response vector and sent to the Rx side for further equalization.

```

% Impulse response reformating

% Reshape LocalImpulse matrix into a vector using RowSize and Aggressors

ImpulseOut(1:RowSize*(Aggressors+1)) = LocalImpulse;

```

#### Reshape Impulse Response and Instantiate Rx System object

Similarly, if you look at the Rx Init code, you can see that the Rx Init function first reshapes the output of the Tx Init function into a 2-D matrix.

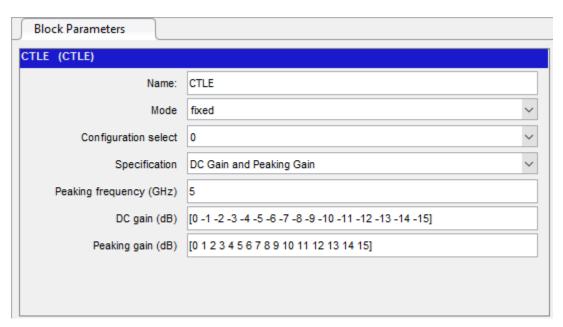

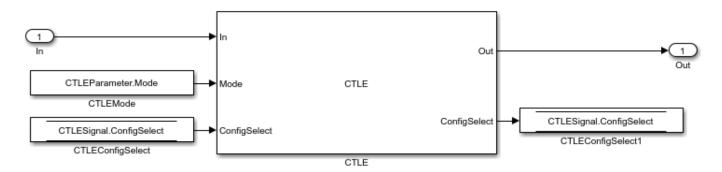

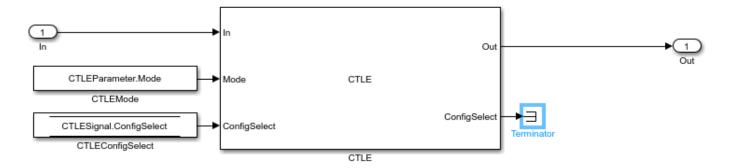

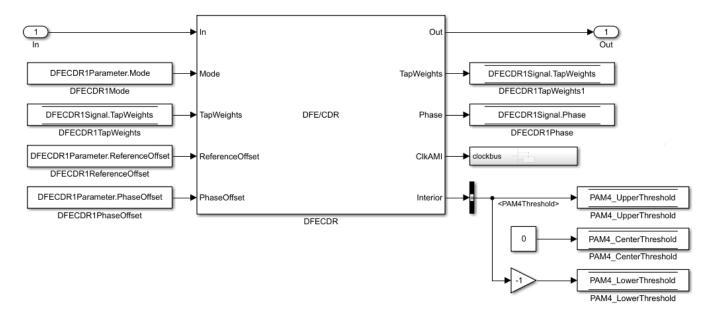

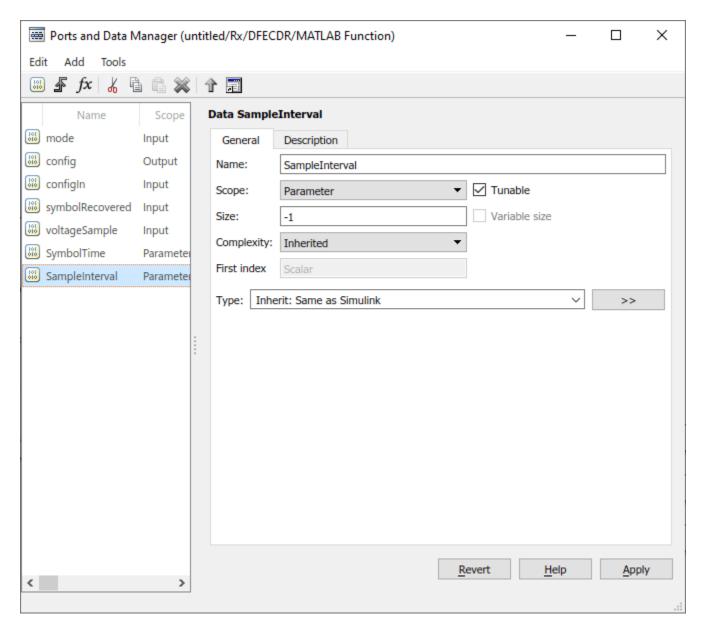

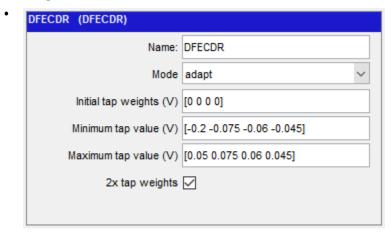

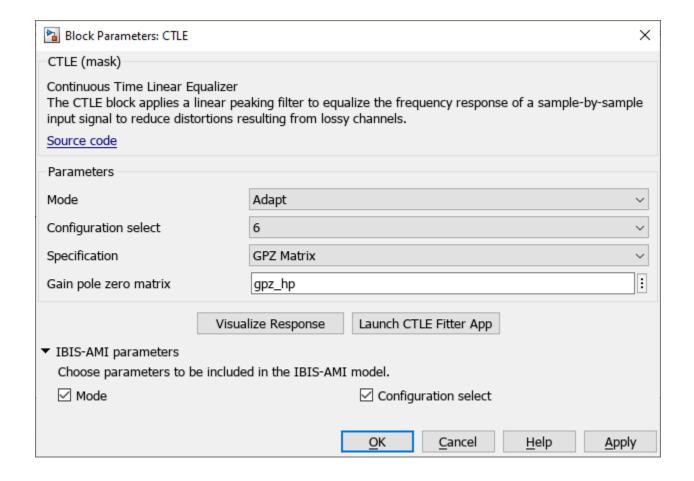

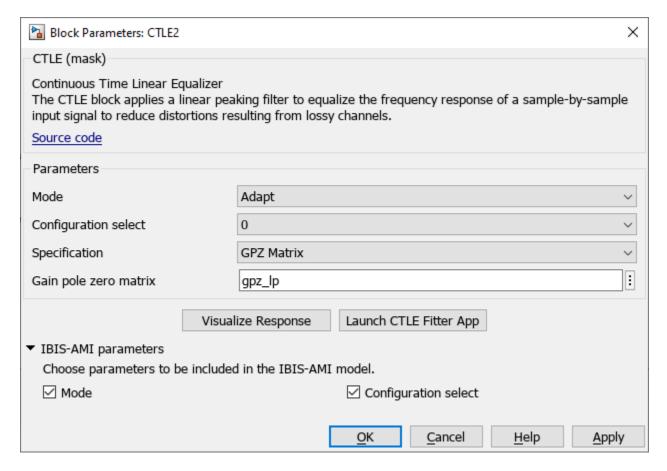

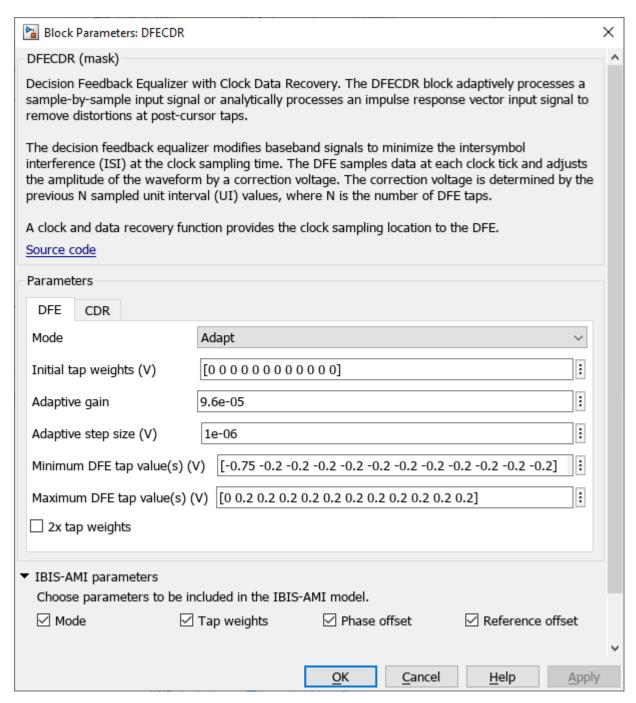

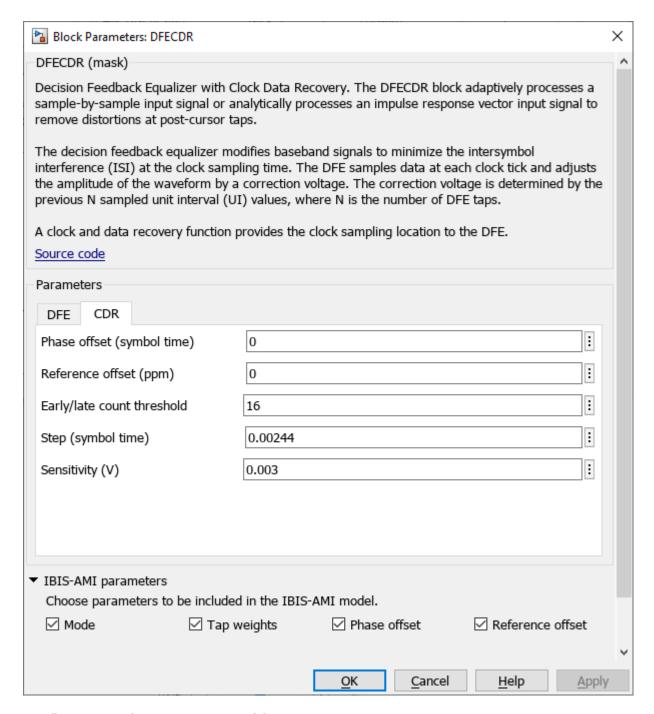

Then the Init function initializes the System objects that represent the blocks on the Rx side and sets up the simulation and AMI parameters and the block properties. In this case, there are two blocks on the Rx side, CTLE and DFECDR.

```

%% Instantiate and setup system objects

% Create instance of serdes.CTLE for CTLE

CTLEInit = serdes.CTLE('WaveType', 'Impulse');

% Setup simulation parameters

CTLEInit.SymbolTime = SymbolTime;

CTLEInit.SampleInterval = SampleInterval;

% Setup CTLE In and InOut AMI parameters

CTLEInit.Mode = CTLEParameter.Mode;

CTLEInit.ConfigSelect = CTLEParameter.ConfigSelect;

% Setup CTLE block properties

CTLEInit.Specification = 'DC Gain and Peaking Gain';

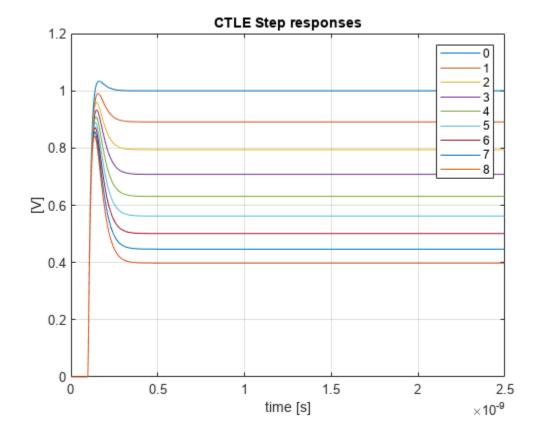

CTLEInit.DCGain = [0 -1 -2 -3 -4 -5 -6 -7 -8];

CTLEInit.ACGain = 0;

CTLEInit.PeakingGain = [0\ 1\ 2\ 3\ 4\ 5\ 6\ 7\ 8];

CTLEInit.PeakingFrequency = 5000000000;

CTLEInit.GPZ = [0 -23771428571 -10492857142 -13092857142;-1 -17603571428 -7914982142 -1334464285

-2 \ -17935714285 \ -6845464285 \ -13596428571; -3 \ -15321428571 \ -5574642857 \ -13848214285; \dots \\

-4 \ -15600000000 \ -4960100000 \ -141000000000; -5 \ -15878571428 \ -4435821428 \ -14351785714; \dots

-6 \ -16157142857 \ -3981285714 \ -14603571428; -7 \ -16435714285 \ -3581089285 \ -14855357142; \dots

-8 -16714285714 -3227142857 -15107142857];

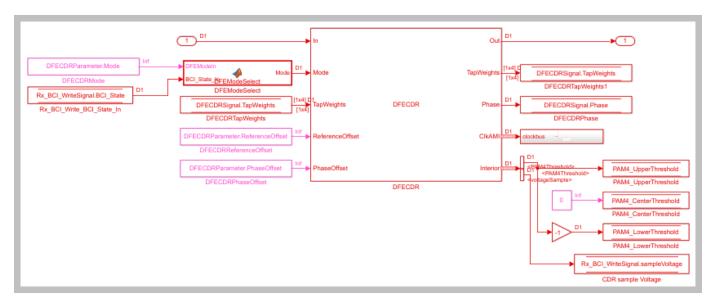

% Create instance of serdes.DFECDR for DFECDR

DFECDRInit = serdes.DFECDR('WaveType', 'Impulse');

% Setup simulation parameters

DFECDRInit.SymbolTime = SymbolTime;

DFECDRInit.SampleInterval = SampleInterval;

DFECDRInit.Modulation = Modulation:

% Setup DFECDR In and InOut AMI parameters

DFECDRInit.ReferenceOffset = DFECDRParameter.ReferenceOffset:

DFECDRInit.PhaseOffset = DFECDRParameter.PhaseOffset;

DFECDRInit.Mode = DFECDRParameter.Mode;

DFECDRInit.TapWeights = DFECDRParameter.TapWeights;

% Setup DFECDR block properties

DFECDRInit.EqualizationGain = 9.6e-05;

DFECDRInit.EqualizationStep = 1e-06;

DFECDRInit.MinimumTap = -1;

DFECDRInit.MaximumTap = 1;

DFECDRInit.Count = 16;

DFECDRInit.ClockStep = 0.0078:

DFECDRInit.Sensitivity = 0;

```

#### **Rx Impulse Response Processing**

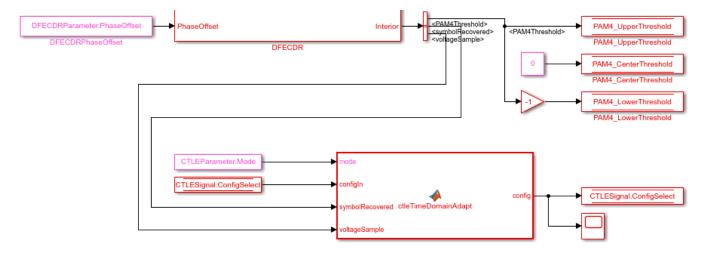

The impulse response that was previously modified by the System objects on the Tx side is then further modified by the System objects on the Rx side.

```

%% Impulse response processing via system objects

% Return impulse response and any Out or InOut AMI parameters for serdes.CTLE instance

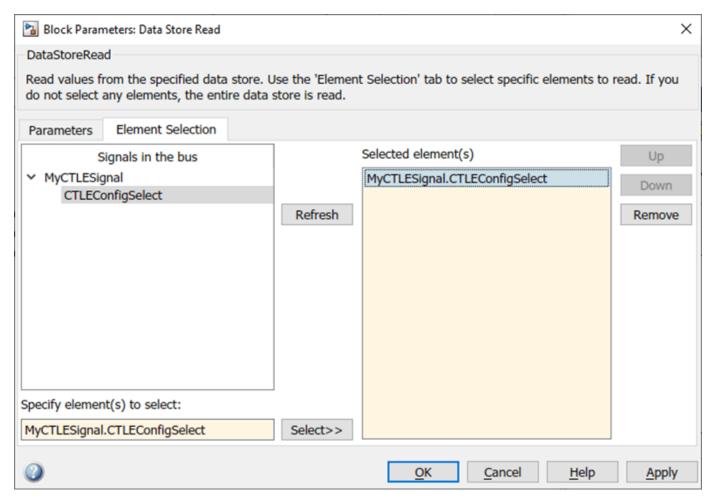

[LocalImpulse, CTLEConfigSelect] = CTLEInit(LocalImpulse);

% Return impulse response and any Out or InOut AMI parameters for serdes.DFECDR instance

[LocalImpulse, DFECDRTapWeights, DFECDRPhase, ~, ~] = DFECDRInit(LocalImpulse);

```

The final equalized impulse response in 2-D matrix form is reshaped back into an impulse response vector.

#### **Custom User Code Area**

Each Init function also contains a section, Custom user code area, where you can customize your own code.

```

%% BEGIN: Custom user code area (retained when 'Refresh Init' button is pressed)

% END: Custom user code area (retained when 'Refresh Init' button is pressed)

```

For more information on how you can use the Custom user code area, see "Customizing Datapath Building Blocks" on page 5-14 and "Implement Custom CTLE in SerDes Toolbox PassThrough Block" on page 5-28.

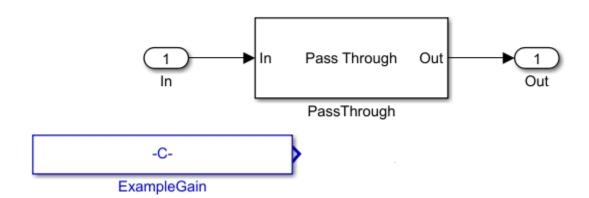

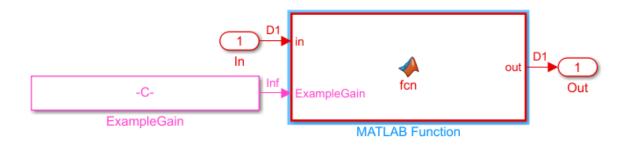

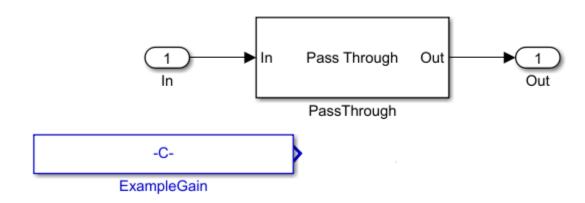

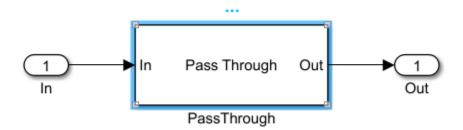

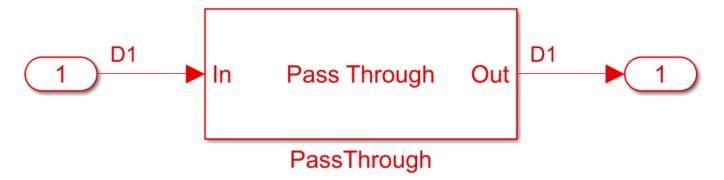

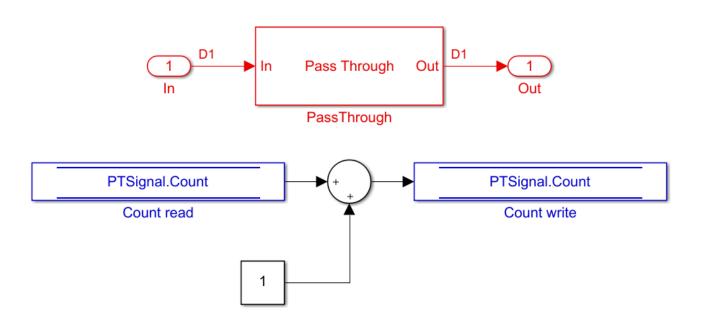

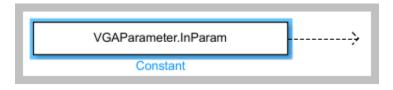

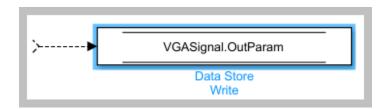

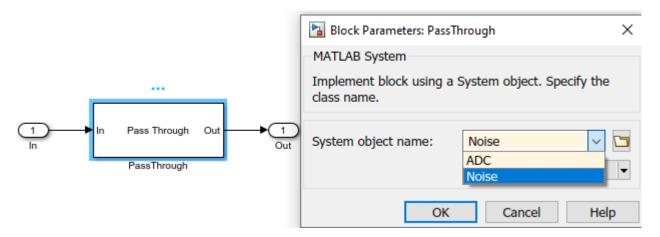

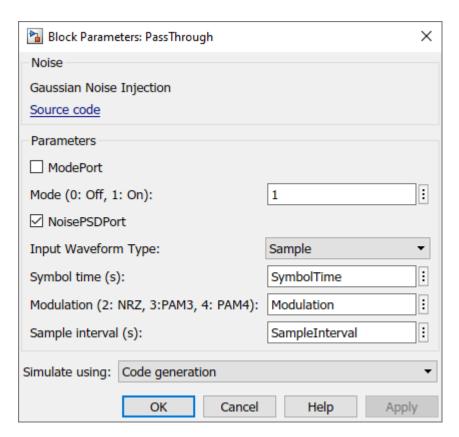

The code generation of Init function (**Refresh Init**) can support one or multiple System objects when using the custom PassThrough block. If multiple system objects are present, they must be in series. The first input port must have a waveform as the input. If any waveform output is present, it must be the first output port.

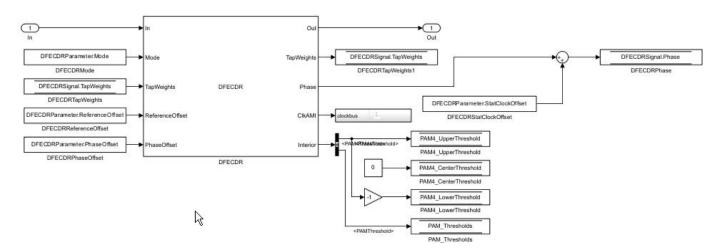

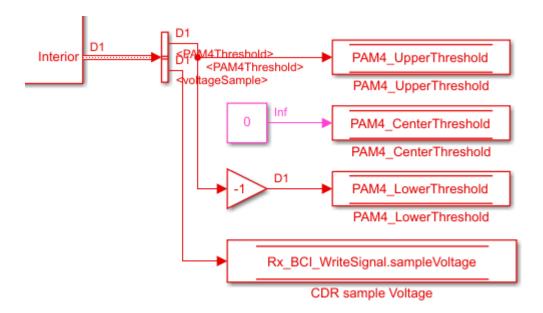

#### **PAMn Thresholds**

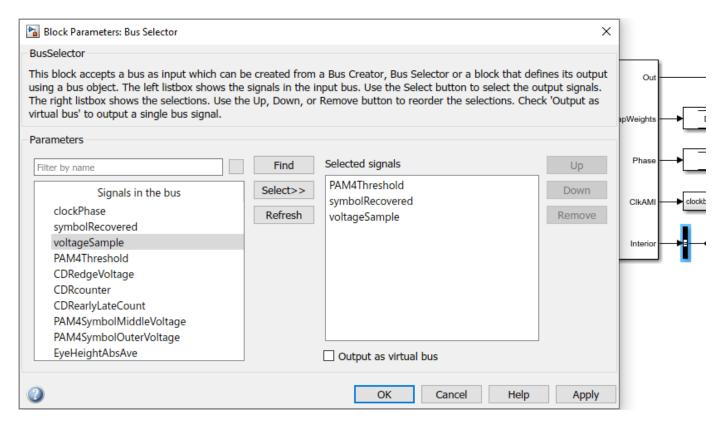

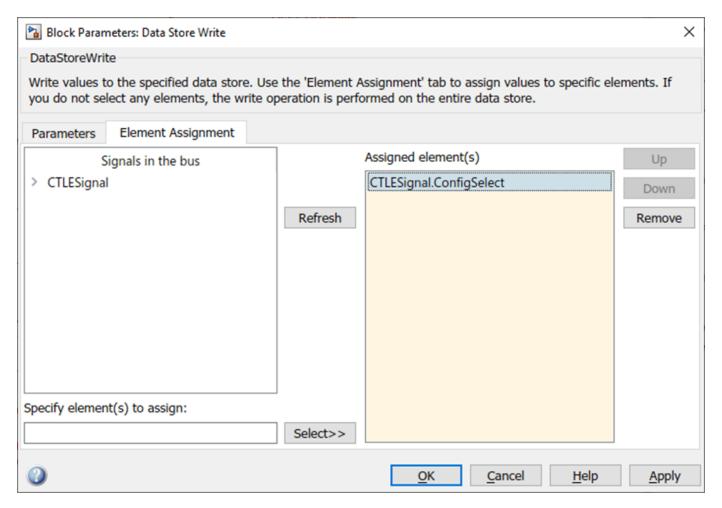

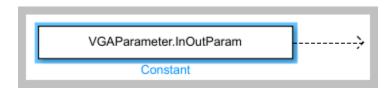

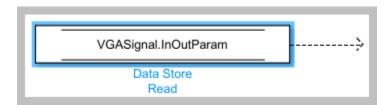

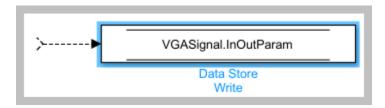

If you are using a SerDes Toolbox datapath library block, PAMn thresholds in the Init function are maintained for you automatically. If you are using a custom configuration using a PassThrough, the code generation of the Init function finds the Data Store Write blocks that reference the PAMn threshold signals (PAMn\_UpperThreshold, PAMn\_CenterThreshold, PAMn\_LowerThreshold) and determines connectivities. The connectivities that are supported are:

- Direct connection to System object

- Connection to System object through bus selector

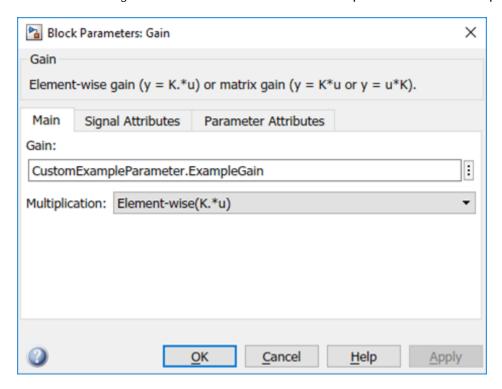

- Connection to System object through Gain block

- · Direct connection to Constant block

If the Init code generation cannot find a supported topology, it applies the default PAM4 thresholds.

## **Advance Init Options**

#### **External Init**

You can export the Init code to an external MATLAB function, customize it, and then use the customized Init function for rapid analysis. To export the Init code, select the **External Init** option in the block parameters dialog box of either the Tx or Rx Init block, then click the **Refresh Init** button. This copies the contents of each of the Init MATLAB function blocks to txInit.m and rxInit.m files and links these functions back to the Simulink model. It also creates a runExternalInit.m file that runs these external Init files in MATLAB.

Once you have customized the Init code and you want to reintegrate the Init function back into the Simulink model, you can disable the **External Init** option and click the **Refresh Init** button again. This copies the contents of the Init function into the default Init files and deletes the external Init files.

#### **Disable Default Impulse Response Processing**

You can comment out the default impulse processing section of the Init code. This option comments out the code preforming the impulse response processing as shown in the "Tx Impulse Response

Processing" on page 1-22 and "Rx Impulse Response Processing" on page 1-23 sections. You can then customize the impulse response processing required for your system design in the "Custom User Code Area" on page 1-24.

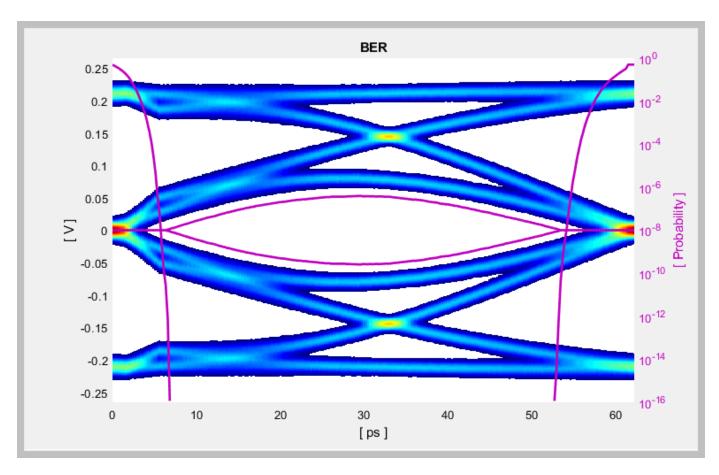

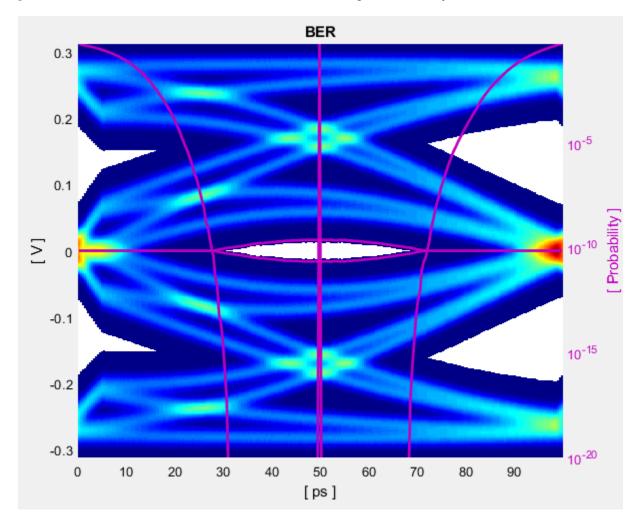

## **Metrics Used in Statistical Analysis**

| <b>Performance Metric</b> | Description                                                                                                                                                                                                                                                            |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eye Height (V)            | Eye height at the center of the BER contour                                                                                                                                                                                                                            |

| Eye Width (ps)            | Eye width of the BER contour                                                                                                                                                                                                                                           |

| Eye Area (V*ps)           | Area inside the BER contour eye                                                                                                                                                                                                                                        |

| Eye Linearity             | Measure of the variance of amplitude separation among different levels of PAM3, PAM4, PAM8, or PAM16, given by the equation: $Linearity = \frac{Minimum \ amplitude \ of \ the \ different \ eye \ levels}{Maximum \ amplitude \ of \ the \ different \ eye \ levels}$ |

| СОМ                       | Channel operating margin, given by the equation: $COM = 20log_{10} \left( \frac{Mean \ eye \ height}{Mean \ eye \ height} \right)$                                                                                                                                     |

| VEC                       | Vertical eye closure, given by the equation: $VEC = \frac{Mean \text{ eye height}}{Inner \text{ eye height}}$                                                                                                                                                          |

#### See Also

#### **More About**

- "Customizing Datapath Building Blocks" on page 5-14

- "Implement Custom CTLE in SerDes Toolbox PassThrough Block" on page 5-28

- "Managing AMI Parameters" on page 6-2

- "Customizing SerDes Toolbox Datapath Control Signals" on page 5-2

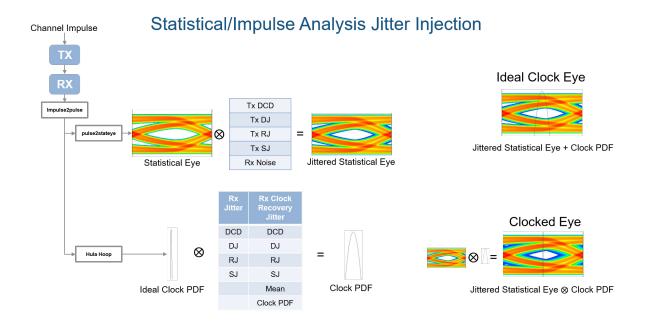

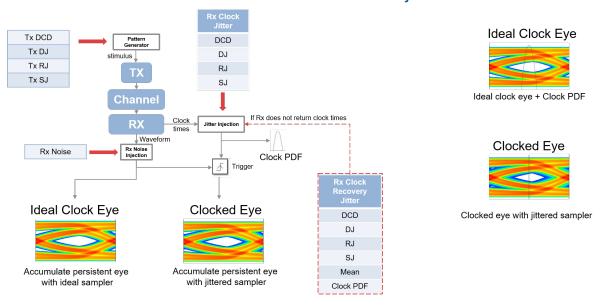

## Jitter Analysis in SerDes Systems

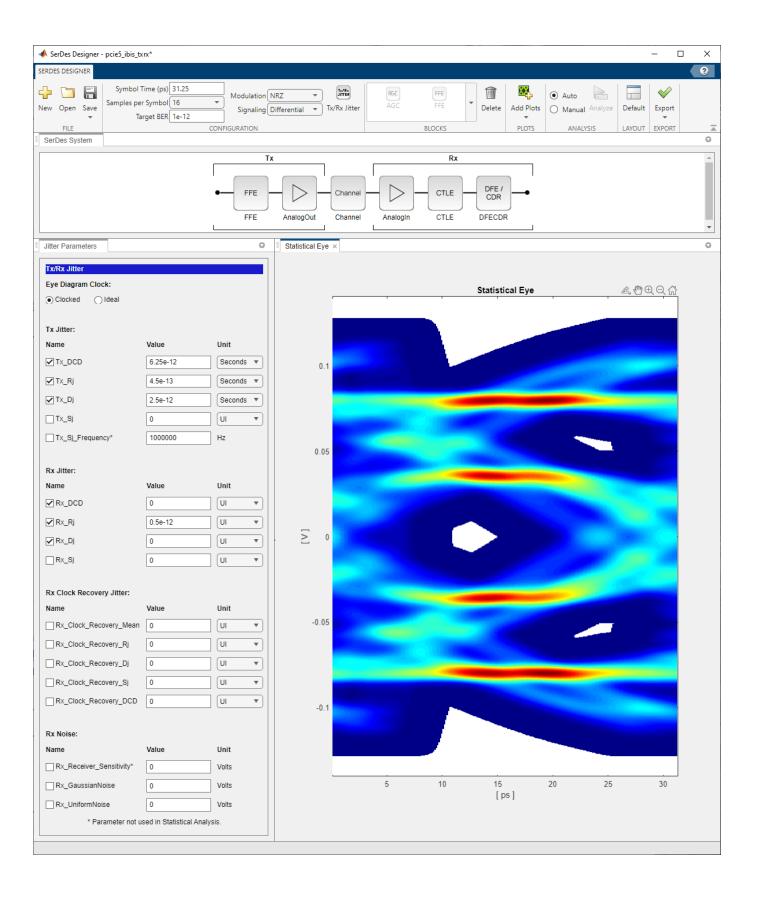

Jitter is an important part of SerDes systems specification. You can include jitter parameters from the **SerDes Designer** app and from the Simulink model. Including jitter impairment in your link and equalization design helps calculate the required eye margins. You can also perform trade-off between different equalization schemes based on total jitter contribution. You can export the jitter values to IBIS-AMI models.

The most common types of jitter are:

| Jitter Type                 | Description                                                                                                                                                                                             |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCD (duty cycle distortion) | Impairment from half and quarter rate clock misalignment. Also known as even-odd jitter.                                                                                                                |

|                             | Duty cycle distortion is defined as the difference in symbol duration between one symbol and the next. The transmitter and receiver duty cycle distortions are half of the clock duty cycle distortion. |

| DJ (deterministic jitter)   | Usually modeled as bounded uniform jitter. Also known as uncorrelated bounded high probability jitter.                                                                                                  |

|                             | Deterministic jitter is defined as half of the peak-to-peak variation.                                                                                                                                  |

| RJ (random jitter)          | Gaussian process that models unbounded jitter events. Also known as uncorrelated unbounded Gaussian jitter.                                                                                             |

|                             | Random jitter is defined as the standard deviation of a white Gaussian phase noise process.                                                                                                             |

| SJ (sinusoidal jitter)      | Bounded periodic jitter that typically comes from power supply voltage variation.                                                                                                                       |

|                             | Sinusoidal jitter is defined as half of the peak-to-<br>peak variation of sinusoidal phase noise<br>amplitude.                                                                                          |

| Noise                       | Random voltage noise. IBIS-AMI 7.0 defines<br>Gaussian noise and uniform noise impairments.<br>Also known as additive white Gaussian noise<br>(AWGN).                                                   |

The expected simulation results vary depending on the type of jitter, injection site (transmitter or receiver), and analysis domain (statistical or time-domain). The **SerDes Designer** app only supports statistical or impulse-based analysis. To perform time-domain analysis, you must export the model to Simulink. The different types of jitter are injected into transmitter and receiver sites according to the IBIS-AMI specifications:

## Time Domain Simulation Jitter Injection

| Normal Mode           | Statistical Analysis                                    | Time Domain Analysis                                            |

|-----------------------|---------------------------------------------------------|-----------------------------------------------------------------|

| Transmitter jitter    | Convolved with eye                                      | Injected in stimulus                                            |

| Receiver jitter       | Convolved with clock PDF (probability density function) | Injected in clock times                                         |

| Clock recovery jitter | Convolved with clock PDF                                | Injected in clock times if receiver does not return clock times |

## See Also **SerDes Designer**

## **External Websites**

https://ibis.org/ver7.0/ver7\_0.pdf

## **Linux Version Compatibilities**

When generating a shared object (.so) file on Linux® platform, MATLAB uses the GLIBC and GLIBCXX (GLIBC++) library versions provided by the operating system (OS). This means that when running these models on an equivalent OS from another vendor, you may encounter compatibility issues which prevent the model from running.

#### **Supported Library Versions for Different OS**

| Linux OS     | GLIBC Library Version | GLIBCXX Library<br>Version | GCC Library Version |

|--------------|-----------------------|----------------------------|---------------------|

| Debian® 9    | 2.24-11               | 3.4.22                     | 6.3                 |

| Debian 10    | 2.28-10               | 3.4.25                     | 8.3                 |

| Red Hat® 6.6 | 2.12                  | 3.4.13                     | 4.4.7               |

| Red Hat 7.7  | 2.17                  | 3.4.19                     | 4.8.5               |

| SUSE® 11.4   | 2.11.3                | _                          | 4.3.4               |

| SUSE 12.3    | 2.19                  | _                          | 4.8                 |

| SUSE 12.4    | 2.22                  | _                          | 4.8                 |

When generating a .so file, the compiler only uses the latest GLIBC/GLIBCXX version for each individual library function. So while the latest Debian 10 GLIBC version is 2.28, SerDes Toolbox only uses a sub-set of the GLIBC libraries. Depending on the blocks being used, it's possible that only v2.12 is required.

For example, a generated .so file for a random Rx AMI model on Debian 10 requires these libraries:

- 0x08922974 0x00 05 GLIBCXX 3.4

- 0x06969194 0x00 04 GLIBC 2.14

- 0x09691a75 0x00 03 GLIBC 2.2.5

- 0x09691a75 0x00 02 GLIBC 2.2.5

This shared object can run on any system with GLIBC v2.14 or later and GLIBCXX v3.4 or later. This means this shared object can run on Red Hat 7.7, but not on Red Hat 6.6.

**Note** This only applies to Linux shared objects. Windows® only requires the Universal C Runtime libraries to be compatible with ALL GLIBC/GLIBCXX versions.

A simple workaround to generate shared objects on an earlier Linux version than what is officially supported in MATLAB is to export the .so file on a fully supported platform, then manually run the build on an earlier version. To do this:

- Go to the transmitter or receiver build directory, denoted by Tx\_ert\_rtw and Rx\_ert\_rtw, respectively.

- From the command line, type the following command:

- make -f Tx.mk

- make -f Rx.mk

The generated shared objects reside one directory above the build directory (.../Tx.so for transmitter and ../Rx.so for receiver.)

• Copy the .so file to the full name used by SerDes Toolbox.

**Note** Manual build of the shared object requires a Simulink Coder or Embedded Coder license.

For a list of supported Linux versions, see Previous Releases: System Requirements and Supported Compilers.

## **See Also**

#### **External Websites**

Windows 10 Universal C Runtime

# **Customize SerDes Systems Topics**

# **Customize SerDes System in MATLAB**

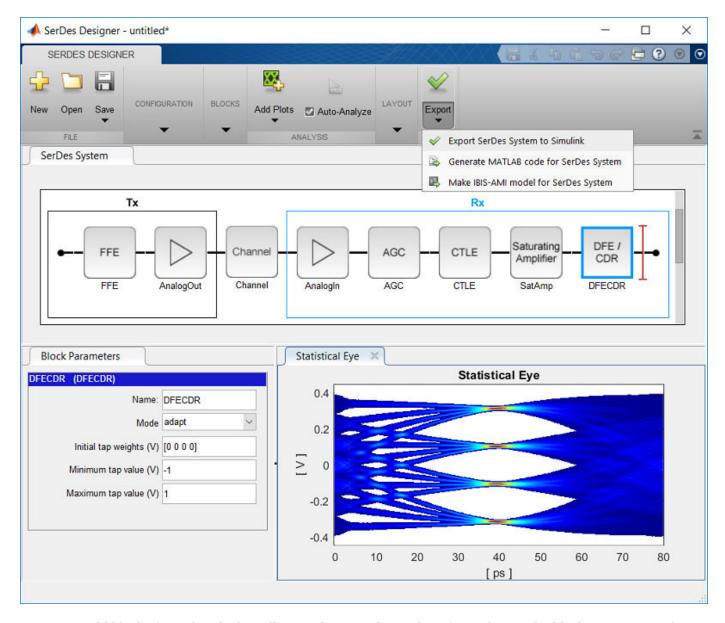

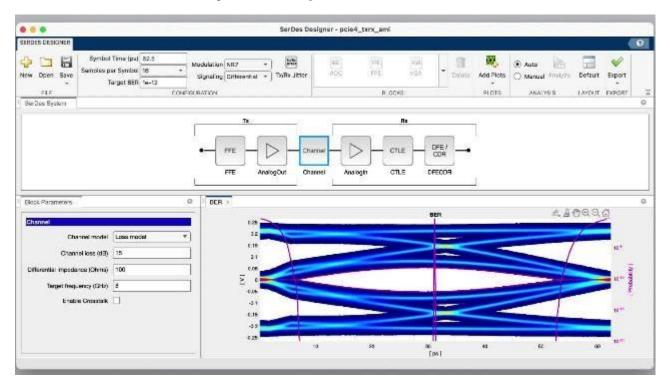

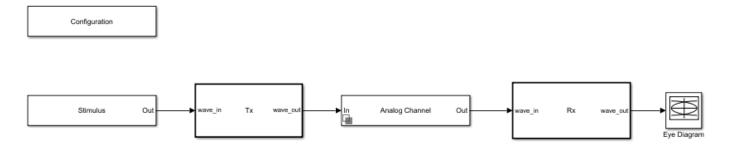

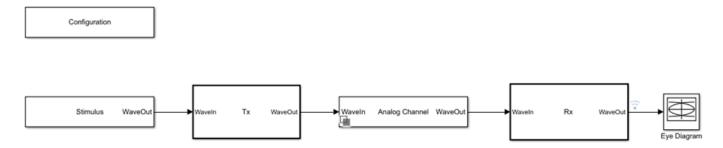

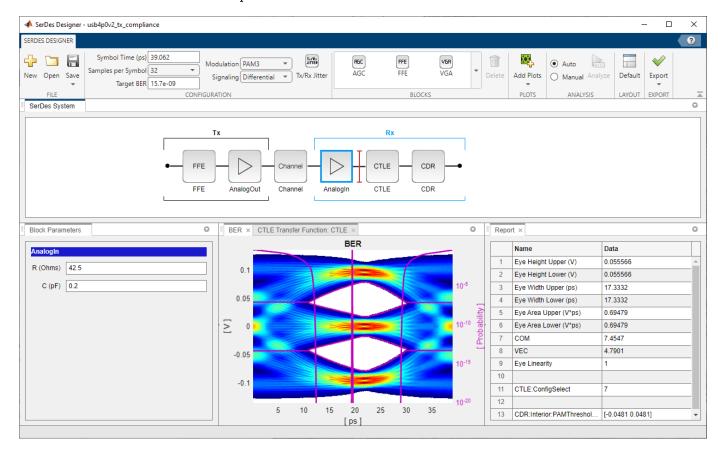

Open the **SerDes Designer** app. In the **CONFIGURATION** tab of the app toolstrip, set **Symbol Time (ps)** to 125 and **Target BER** to 1e-12.

In a new blank canvas, add an FFE block to the Tx side. Add an AGC, a CTLE and a DFECDR block to the Rx side.

Select the channel block. Set Channel loss (dB) to 13.

From the **EXPORT** tab of the app toolstrip, select **Generate MATLAB code for SerDes System**. A MATLAB script open that represents the command line interface to the SerDes system.

The MATLAB script contains the code to generate the transmitter and receiver building blocks and analog models. It also contains the channel information and SerDes system configuration. The script exposes every parameter that is part of the SerDes system. You can modify the parameters to further explore the SerDes system.

For example, to see the effect of **Channel loss** on the SerDes system, scroll down to the section of the MATLAB script that says % Build ChannelData. Replace the default code section with the following code:

```

% Build ChannelData:

channelLoss = 5;

channel = ChannelData( ...

'ChannelLossdB', channelLoss, ...

'ChannelLossFreq',5000000000, ...

'ChannelDifferentialImpedance',100);

```

Save the change and run the script. Keep changing the value of channelloss to see the effect of changing channel loss.

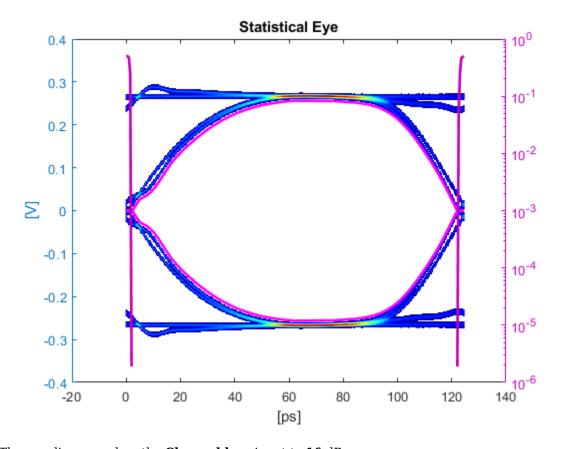

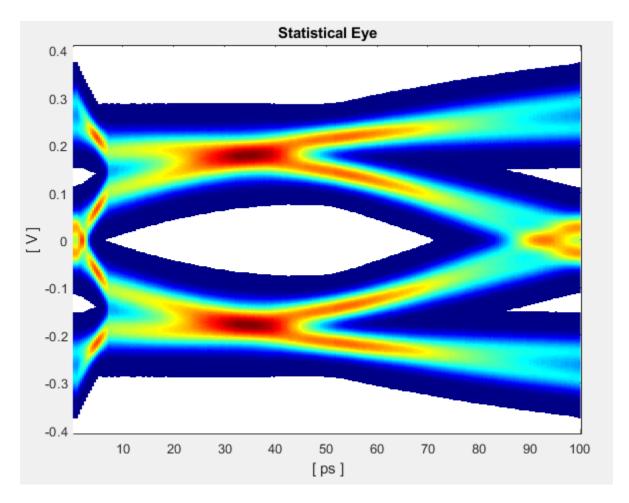

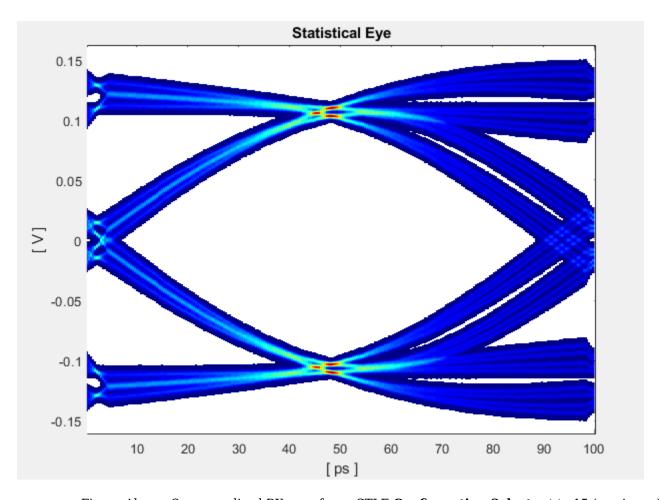

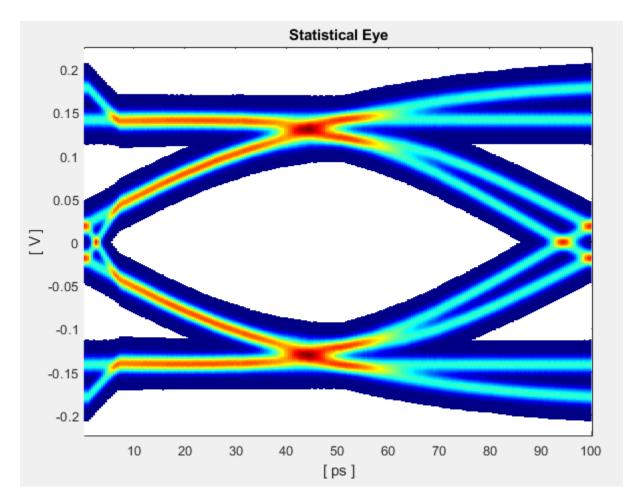

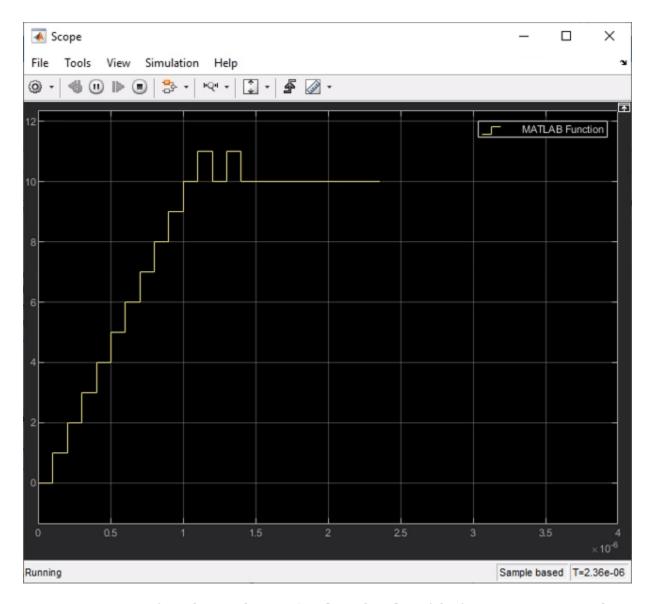

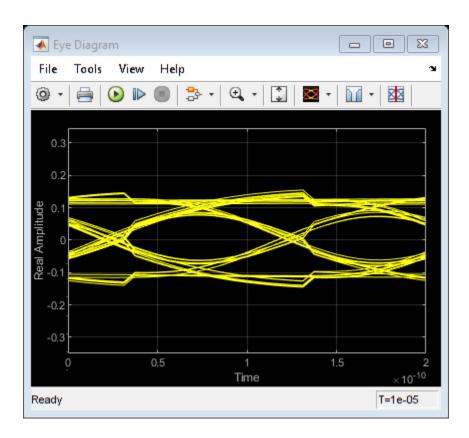

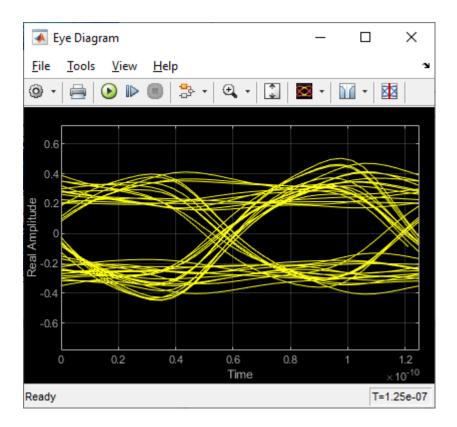

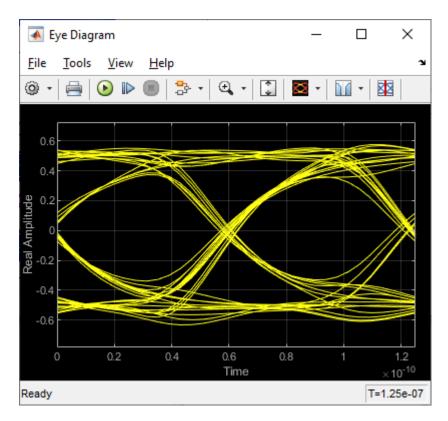

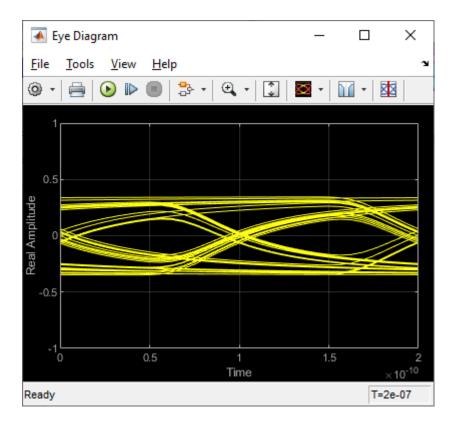

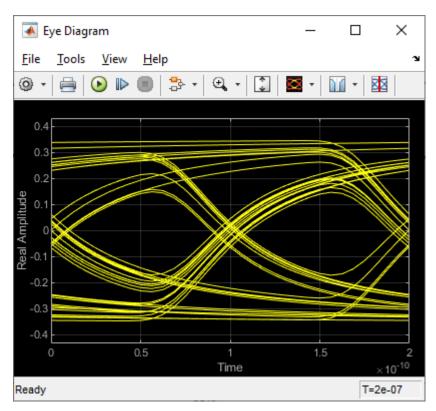

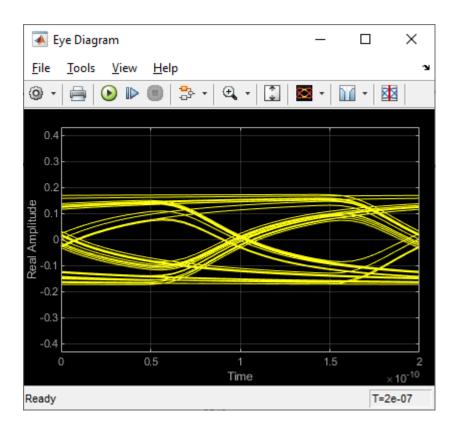

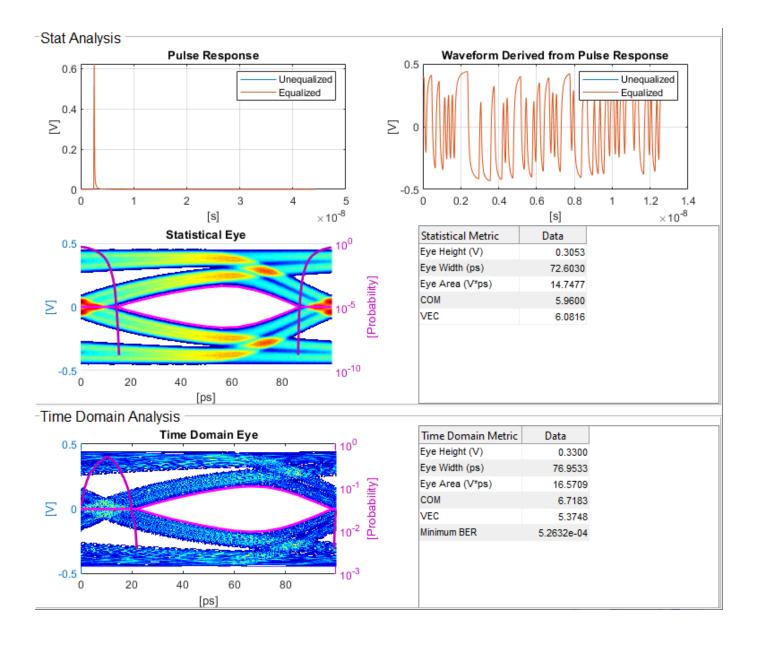

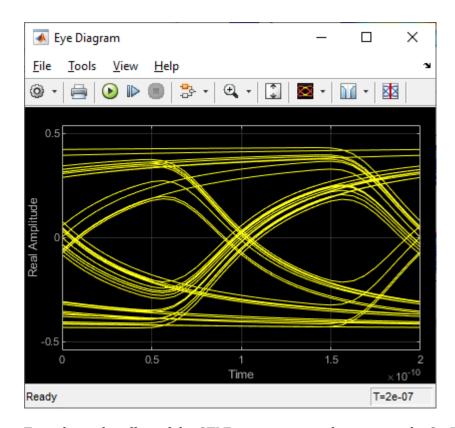

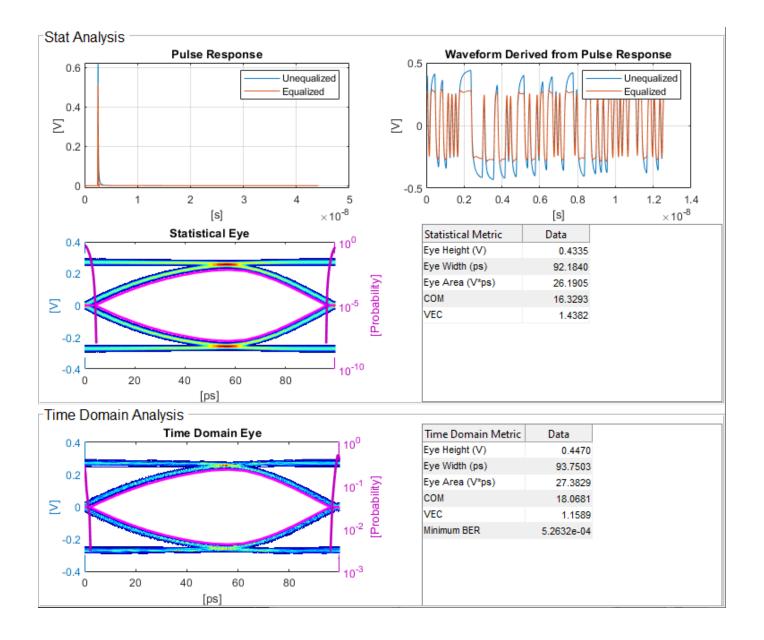

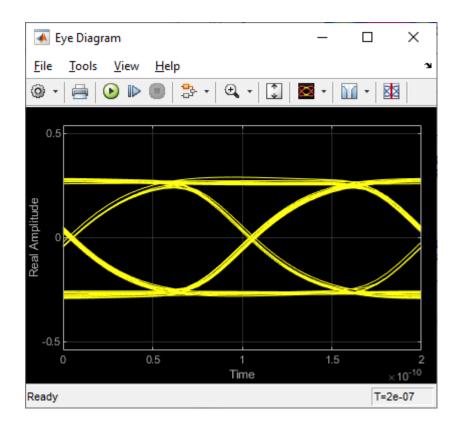

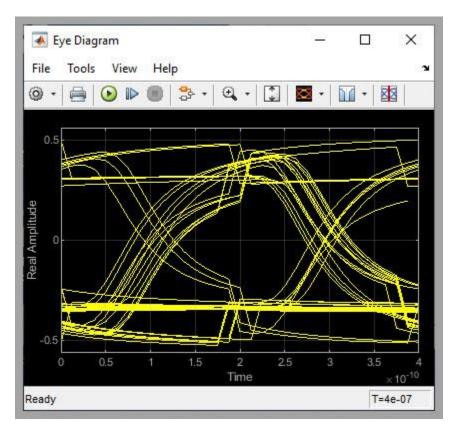

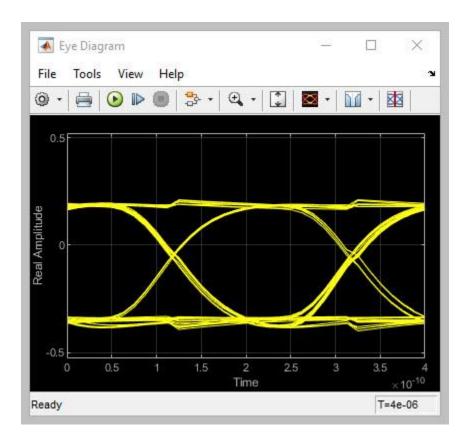

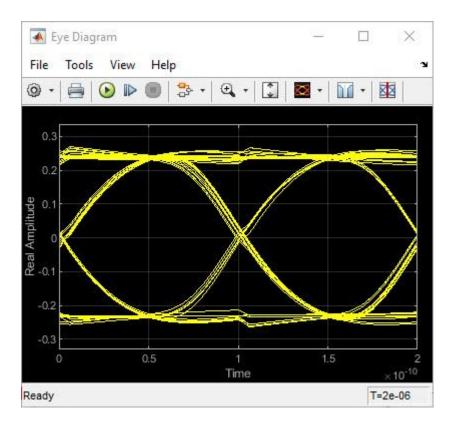

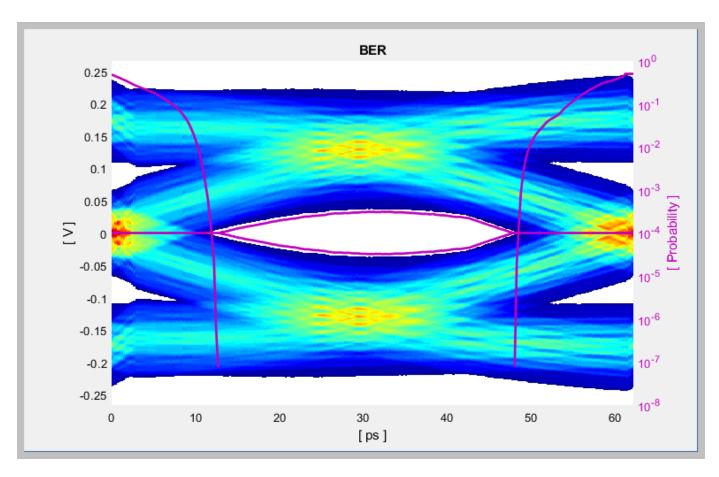

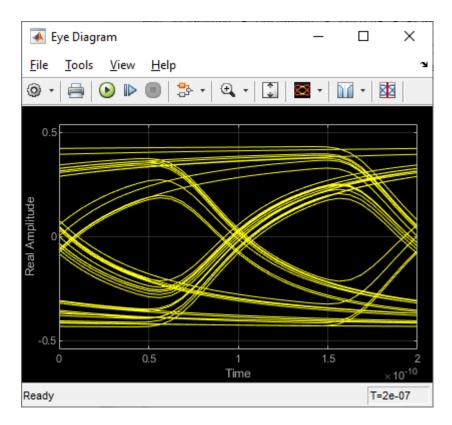

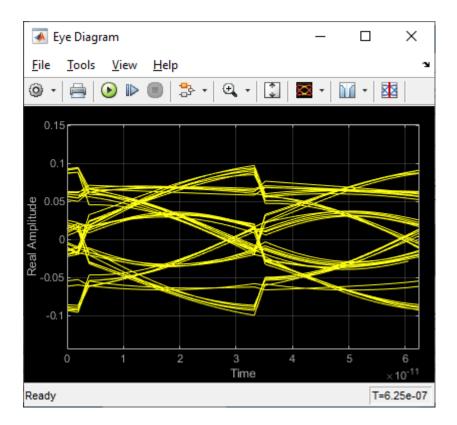

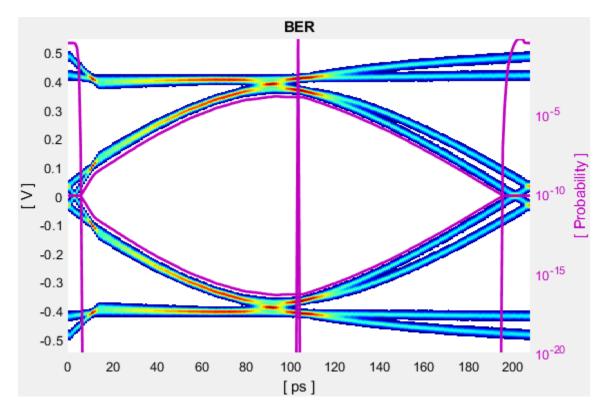

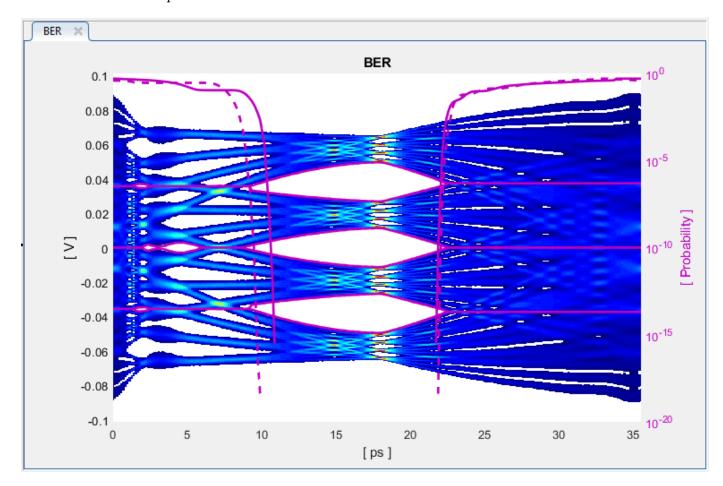

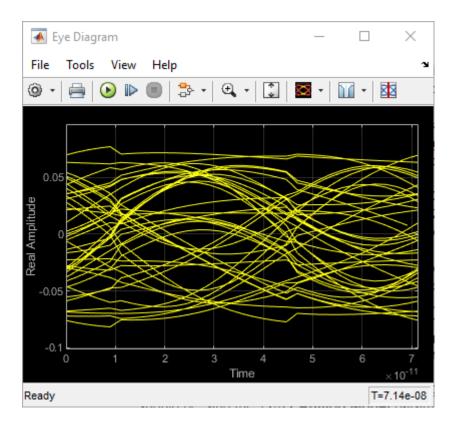

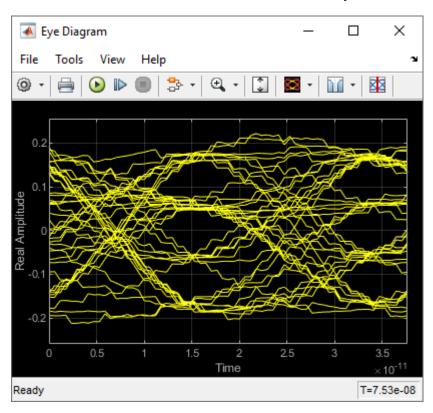

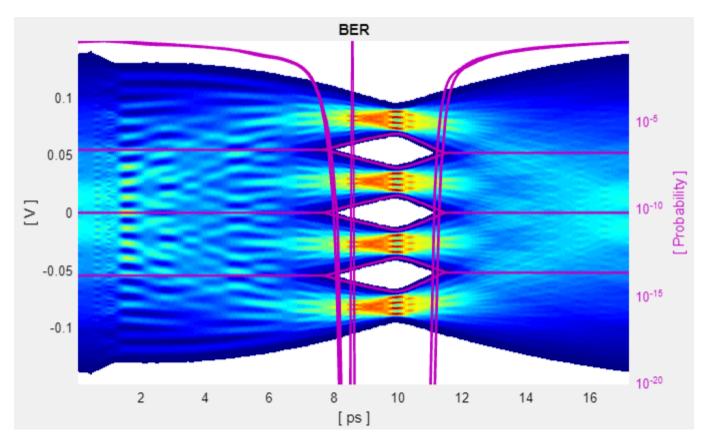

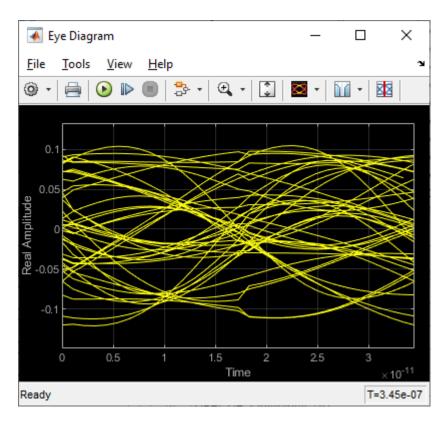

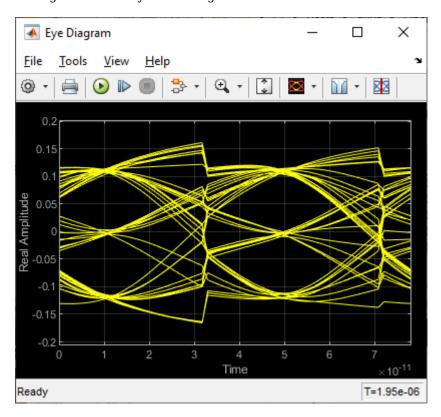

The eye diagram when the **Channel loss** is set to 5 dB:

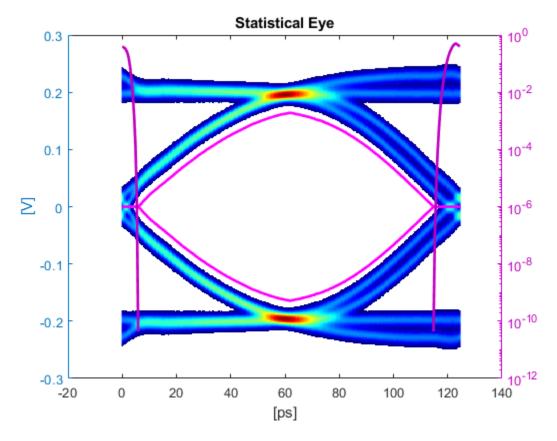

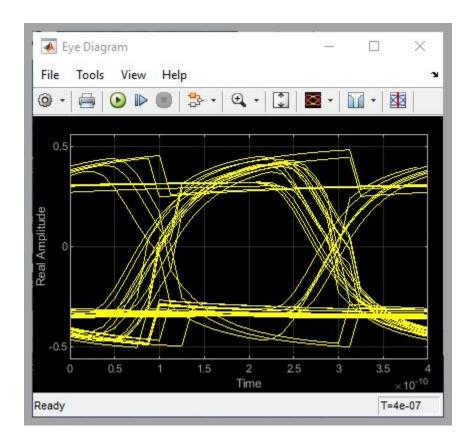

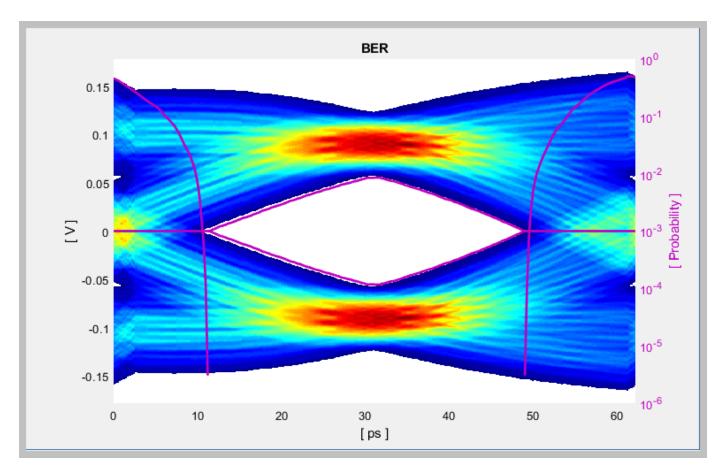

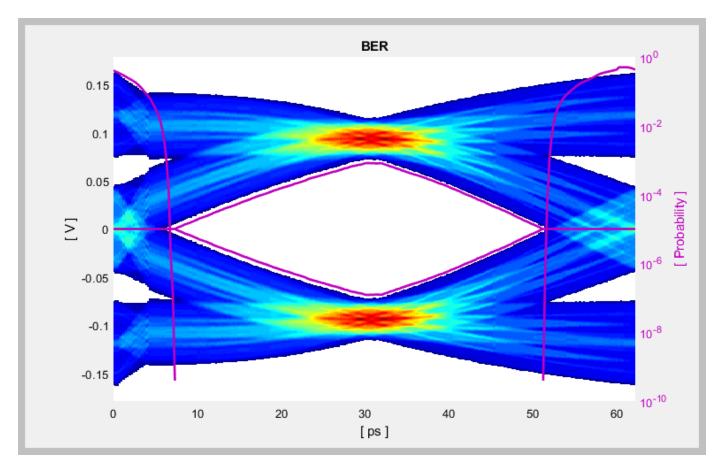

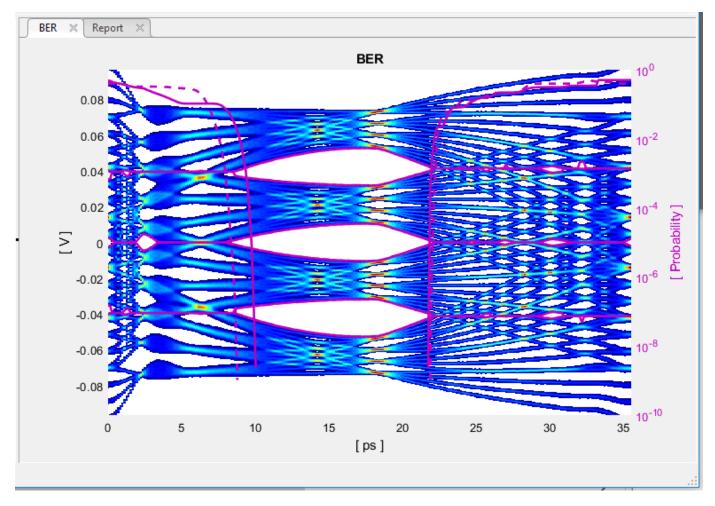

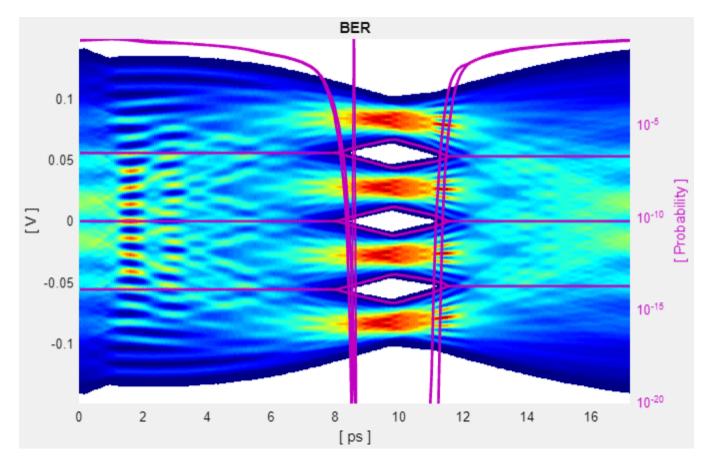

The eye diagram when the  ${\bf Channel\ loss}$  is set to 16 dB:

After you finalize the SerDes system with your desired Channel Loss, you can export the MATLAB script of the SerDes system as a Simulink model. From the Simulink canvas, you can perform further time-domain analysis, or export the system to a AMI model.

## **See Also**

SerDes Designer | serdes.ChannelLoss | FFE | AGC | DFECDR | CTLE

# **Create and Customize IBIS-AMI Models Topics**

- "SiSoft Link" on page 3-2

- "SerDes Toolbox Interface for SiSoft Quantum Channel Designer and QSI Software" on page 3-3

- "Signal Integrity Link" on page 3-11

## SiSoft Link

**Note** The SiSoft Link app is not recommended. Use "Signal Integrity Link" on page 3-11 instead.

The SiSoft Link app is used to test the SerDes models developed in Simulink using SerDes Toolbox in SiSoft Quantum Channel Designer (QCD) and Quantum Signal Integrity (QSI) software. You can transfer the data required to reproduce a QCD or QSI test case back to Simulink® for debugging and refinement. You need SiSoft 2018.07-SP4 or later software.

Using the SiSoft Link app, you can:

- · Create a QCD project.

- · Create a QSI project.

- Import QCD or QSI simulation data into Simulink.

- Update QCD or QSI with new data from Simulink.

To test the SerDes model in QSI or QCD software, first download the SerDes Toolbox Interface for SiSoft Quantum Channel Designer and QSI Software from the Add-On Explorer. For more information on downloading add-ons, see "Get and Manage Add-Ons".

To access the SiSoft link app:

- From the Apps tab in the MATLAB toolstrip, click on SiSoft Link app icon.

- In the MATLAB command prompt, enter sisoftLink.

#### See Also

#### **More About**

"SerDes Toolbox Interface for SiSoft Quantum Channel Designer and QSI Software" on page 3-3

# SerDes Toolbox Interface for SiSoft Quantum Channel Designer and QSI Software

This example shows how to use SerDes Toolbox Interface for SiSoft Quantum Channel Designer and QSI Software support package to test IBIS-AMI SerDes models developed in Simulink using SerDes Toolbox, in SiSoft Quantum Channel Designer (QCD) or Quantum Signal Integrity (QSI) software. You can transfer the data required to reproduce a QCD or QSI test case back to Simulink for debugging and refinement. You need SiSoft 2018.07-SP4 or later software to run this example. You must also have installed the SiSoft Link app provided with the support package.

**Note** SerDes Toolbox Interface for SiSoft Quantum Channel Designer and QSI Software is not recommended. Use "Signal Integrity Link" on page 3-11 instead.

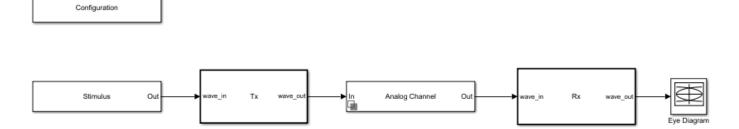

#### **SerDes Development Flow**

SerDes model development begins with the SerDes Designer app. The app exports a Simulink model with transmitter (Tx) and receiver (Rx) SerDes models and a testbench to simulate and further develop the SerDes designs. Test the models in QCD or QSI to verify proper IBIS-AMI model operation in a target EDA tool. Due to the high performance of IBIS-AMI executable models, run many simulations to verify the full range of model capabilities, testing with all possible AMI parameters and a variety of stimuli and interconnect channels. Replicate the simulation cases warranting closer inspection in Simulink to reproduce and debug the test. Repeat this cycle as many times as needed, updating the QCD/QSI project and Simulink model.

#### **Create SerDes Toolbox System Model**

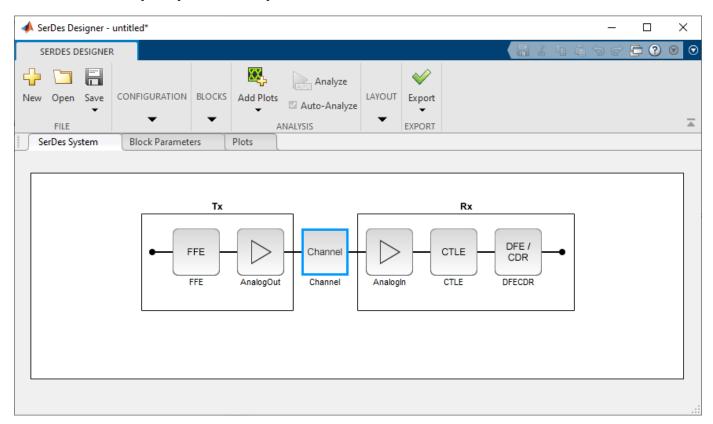

Open the **SerDes Designer** app from the Apps toolstrip. Use the app to quickly prototype and statistically analyze a SerDes system with a Tx and an Rx.

Add blocks from the Blocks gallery to the Tx and Rx sides. If you change the block parameters, the statistical eye display shows the performance changes. Click on **Export SerDes System to Simulink** from the Export dropdown menu to create a Simulink model for the system.

#### **Prepare SerDes Simulink Model for QCD/QSI**

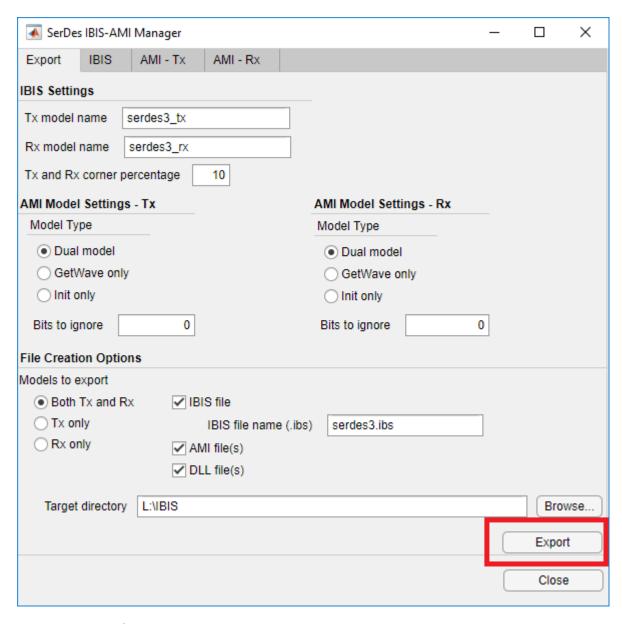

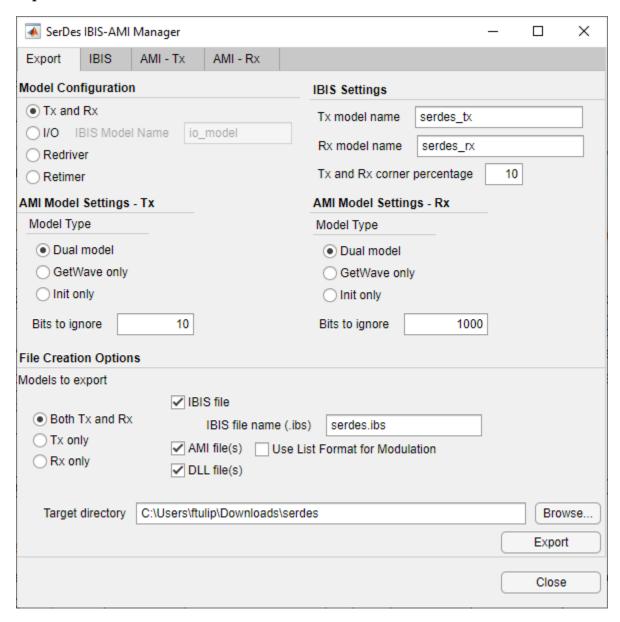

The SiSoft QCD and QSI software requires IBIS models to simulate the Tx and Rx of your system. Use the "Open SerDes IBIS-AMI Manager" button in the Configuration block to produce the IBIS files. In the **Export** tab of the SerDes IBIS-AMI Manager dialog box choose a target directory and click the **Export** button to create the set of IBIS files.

#### **Create QCD Project**

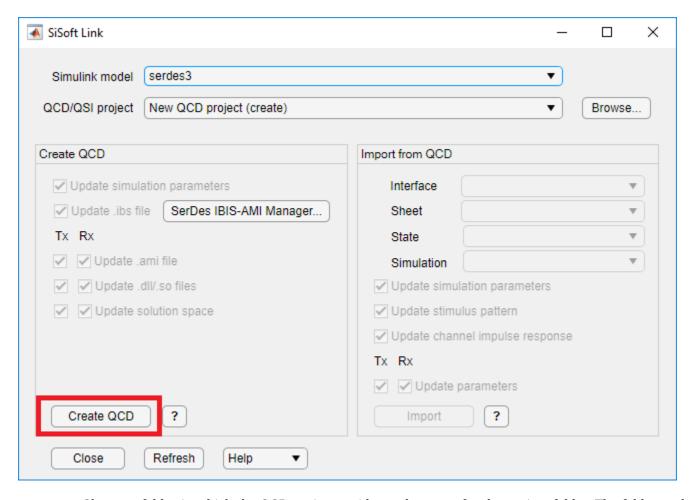

Click the SiSoft Link icon from the Apps tab in the MATLAB toolstrip to open the SiSoft Link app.

If your SerDes system model is open in Simulink, it is listed in the **Simulink Model** dropdown menu in the SiSoft Link app. Click the **Refresh** button if your model is not listed. Set the **QCD/QSI project** dropdown menu to New QCD project (create) and click **Create QCD**. If there are unresolved issues regarding the selected Simulink model, **Create QCD** button remains disabled.

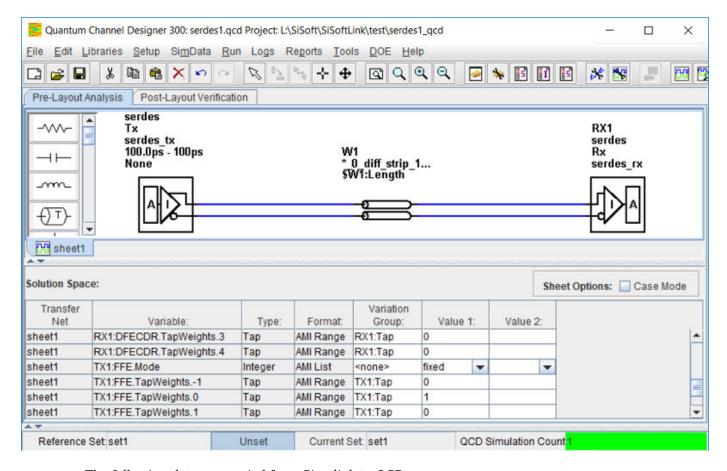

Choose a folder in which the QCD project resides and a name for the project folder. The folder path and project name must not have spaces. If you have not yet used SiSoft Link to create a project, the system asks you to locate the folder containing your SiSoft software. A report window appears and QCD opens executing a script produced by SiSoft Link. When script execution finishes, the QCD project interface is renamed after your SerDes system model, with a single sheet sheet1.

The following data are copied from Simulink to QCD:

- The QCD interface has the same name as the Simulink model.

- OCD has one sheet, sheet1.

- All IBIS files is copied into the QCD project si lib/ibis folder.

- All Tx and Rx model parameter values from Simulink is set in the QCD solution space.

- Simulation parameters are set: **UI**, **Samples\_Per\_Bit**, and **TargetBER**.

#### **Create QSI Project**

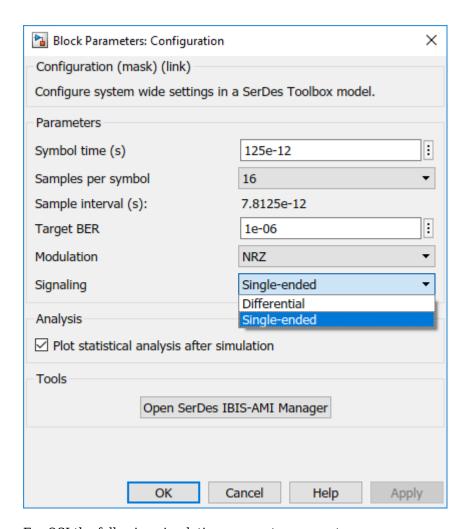

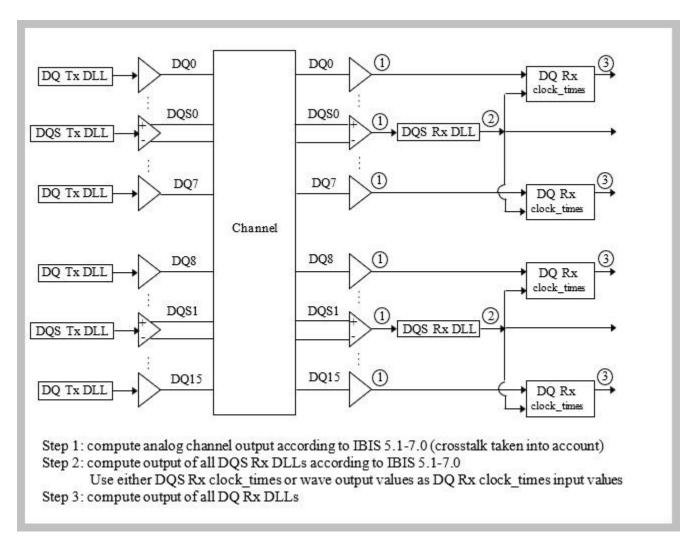

To create a QSI project, set the **QCD/QSI project** dropdown menu to New QSI project (create) and click the **Create QSI** button. The process is otherwise similar to that for QCD. Typically, IBIS-AMI models are used in QSI for analysis of single-ended DDR4/5 DQS signals with equalization. If that is the case, double click the Configuration block in the Simulink model to open it, and set **Signaling** to Single-ended before creating the QSI project.

For QSI the following simulation parameters are set:

- The OSI interface has the same name as the Simulink model.

- QSI has one sheet, sheet1.

- All IBIS files is copied into the QSI project si lib/ibis folder.

- All Tx and Rx model parameter values from Simulink is set in the QSI solution space.

- Simulation parameters are set: UI, Samples\_Per\_Bit, and TargetBER.

- The Tx **rise\_time** is copied from the typical corner value in the IBIS file.

- Time Domain Stop is set to Ignore Bits + 20,000 UI.

- Record\_Bits is set to 100 and Record\_Start is set accordingly.

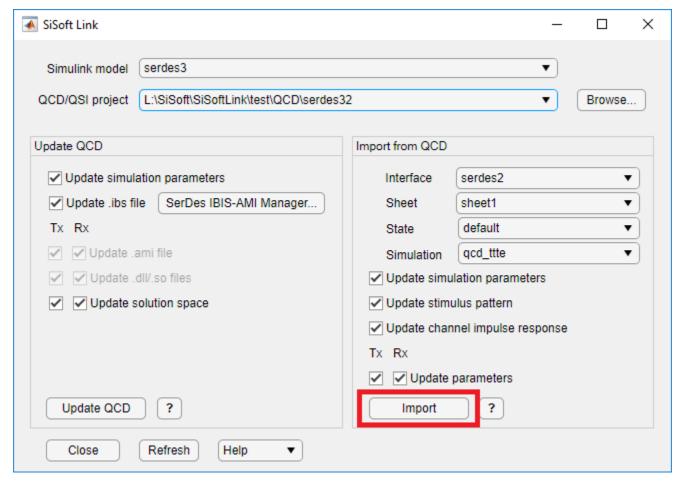

#### Import QCD or QSI Simulation Data into Simulink

After simulating in QCD or QSI, you can import data to reproduce a simulation in Simulink. You must select the project in the **QCD/QSI project** dropdown menu. Click the **Browse...** button to choose a desired QCD or QSI project if it is not listed in the **QCD/QSI project** dropdown menu.

The following data are copied from QCD/QSI to Simulink, as enabled by the Import section checkboxes:

- All Tx and Rx model parameter values from the selected simulation are set in corresponding blocks in the Simulink model.

- Modulation, SymbolTime, and SampleInterval are set in the Configuration block.

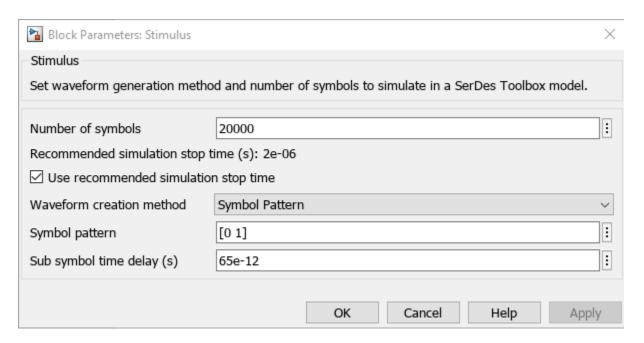

- The time domain stimulus pattern is set in the Stimulus block, even if only statistical simulations are run in QCD/QSI.

- The channel impulse response from QCD/QSI is set in the Analog Channel block.

A report is generated giving the details of the import.

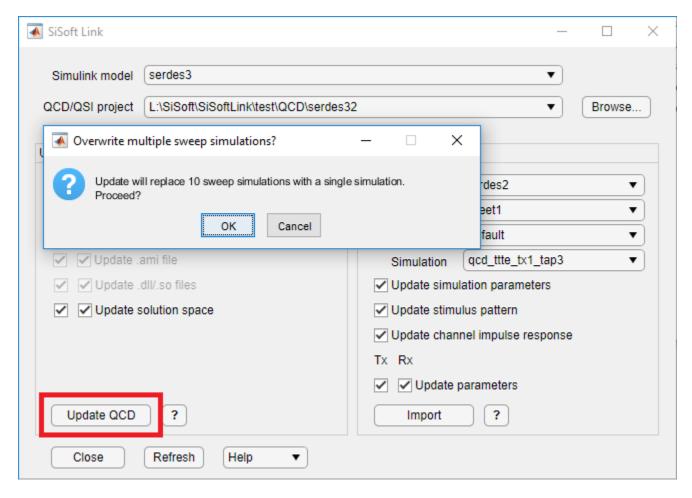

#### Update QCD or QSI with New Data from Simulink

To support iterative development, selectively update a QCD or QSI project with data from Simulink. When a QCD or QSI project path is selected in **QCD/QSI project** dropdown menu, the **Create QCD** (or **Create QSI**) button becomes **Update QCD** (or **Update QSI**). The checkboxes above the button are enabled to choose the data to be updated. If **Update .ibs** file is checked, the checkboxes for .ami files and .dll/.so files are forced on, since importing the .ibis file in QCD or QSI always imports the other files along with it.

Clicking **Update QCD** (or **Update QSI**) runs the QCD (or QSI) to open the project and makes the changes. To avoid conflicts, you must close the project before updating it.

#### See Also

**SerDes Designer** | Analog Channel | Stimulus | Configuration

#### **More About**

"SiSoft Link" on page 3-2

# **Signal Integrity Link**

This example shows how to test the IBIS-AMI SerDes models developed in SerDes Toolbox using the Signal Integrity Toolbox $^{\text{TM}}$ . You need a license to Signal Integrity Toolbox.

#### **SerDes Development Flow**

SerDes model development begins with the **SerDes Designer** app. The app exports a Simulink model with transmitter (Tx) and receiver (Rx) SerDes models and a testbench to simulate and further develop the SerDes designs. Test the models in the Signal Integrity Toolbox to verify proper IBIS-AMI model operation in a target EDA tool. Due to the high performance of IBIS-AMI executable models, run many simulations to verify the full range of model capabilities, testing with all possible AMI parameters and a variety of stimuli and interconnect channels. Replicate the simulation cases warranting closer inspection in Simulink to reproduce and debug the test. Repeat this cycle as many times as needed, updating the .qcd/.edk project files and Simulink model.

#### **Create SerDes Toolbox System Model**

Open the **SerDes Designer** app from the Apps toolstrip. Use the app to quickly prototype and statistically analyze a SerDes system with a Tx and an Rx.

Add blocks from the Blocks gallery to the Tx and Rx sides. If you change the block parameters, the statistical eye display shows the performance changes. Click on **Export SerDes System to Simulink** from the Export dropdown menu to create a Simulink model for the system.

#### **Prepare SerDes Simulink Model for Signal Integrity Toolbox**

The Signal Integrity Toolbox requires IBIS models to simulate the Tx and Rx of your system. Use the "Open SerDes IBIS-AMI Manager" button in the Configuration block to produce the IBIS files. In the **Export** tab of the SerDes IBIS-AMI Manager dialog box choose a target directory and click the **Export** button to create the set of IBIS files.

#### **Serial Link Project**

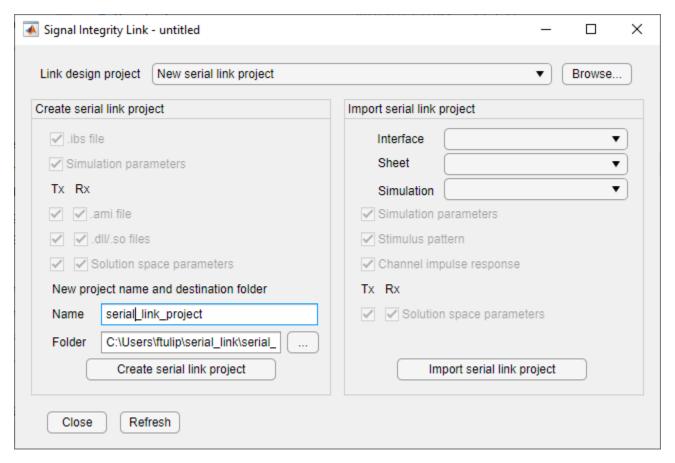

Click the "Open Signal Integrity Link" button in the Configuration block. In the newly opened dialog box, select New serial link project from the dropdown menu of **Link design project** parameter.

Choose a project name and destination folder. The folder path and project name must not have spaces. A report window appears and the **Serial Link Designer** app opens to create serial link project from SerDes Toolbox model.

The following data are copied from Simulink to Serial Link Designer:

- The Serial Link Designer interface has the same name as the Simulink model.

- Serial Link Designer has one sheet, sheet1.

- All IBIS files is copied into the serial link project si\_lib/ibis folder.

- All Tx and Rx model parameter values from Simulink is set in the **Serial Link Designer** solution space.

- Simulation parameters are set: **UI**, **Samples Per Bit**, and **TargetBER**.

Once you create the serial link project, you can refresh the Signal Integrity Link to see your project from the **Link design project** parameter dropdown menu. You can make updates to existing project or import a new project from a simulation of an already simulated project.

#### **Parallel Link Project**

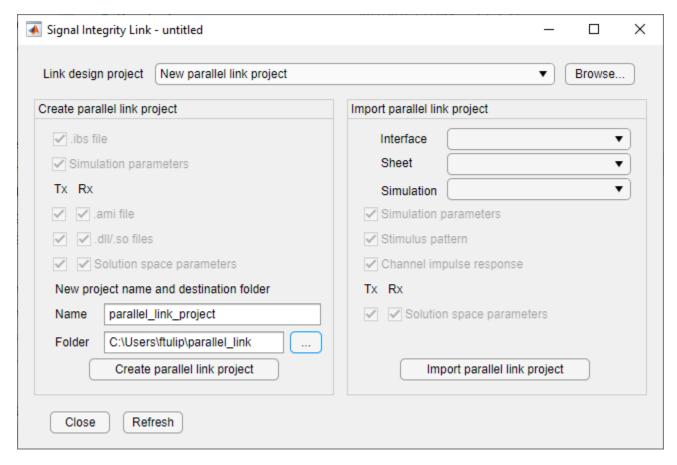

Click the "Open Signal Integrity Link" button in the Configuration block. In the newly opened dialog box, select New parallel link project from the dropdown menu of **Link design project** parameter.

Choose a project name and destination folder. The folder path and project name must not have spaces. A report window appears and the **Parallel Link Designer** app opens to create parallel link project from SerDes Toolbox model.

The following data are copied from Simulink to Parallel Link Designer:

- The **Parallel Link Designer** interface has the same name as the Simulink model.

- Parallel Link Designer has one sheet, sheet1.

- All IBIS files is copied into the parallel link project si lib/ibis folder.

- All Tx and Rx model parameter values from Simulink is set in the **Parallel Link Designer** solution space.

- Simulation parameters are set: UI, Samples Per Bit, and TargetBER.

Once you create the parallel link project, you can refresh the Signal Integrity Link to see your project from the **Link design project** parameter dropdown menu. You can make updates to existing project or import a new project from a simulation of an already simulated project.

#### See Also

**SerDes Designer** | Analog Channel | Stimulus | Configuration | **Serial Link Designer** | **Parallel Link Designer**

# Design and Simulate SerDes Systems Examples

- "Find Zeros, Poles, and Gains for CTLE from Transfer Function" on page 4-2

- "Convert Scattering Parameter to Impulse Response for SerDes System" on page 4-21

- "Globally Adapt Receiver Components Using Pulse Response Metrics to Improve SerDes Performance" on page 4-27

- "Globally Adapt Receiver Components in Time Domain" on page 4-32

- "Model Clock Recovery Loops in SerDes Toolbox" on page 4-52

- "Phase Detectors: Baud-Rate Type-A versus Bang-Bang" on page 4-78

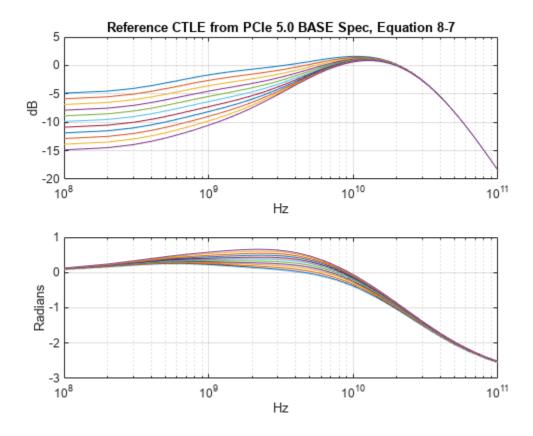

## Find Zeros, Poles, and Gains for CTLE from Transfer Function

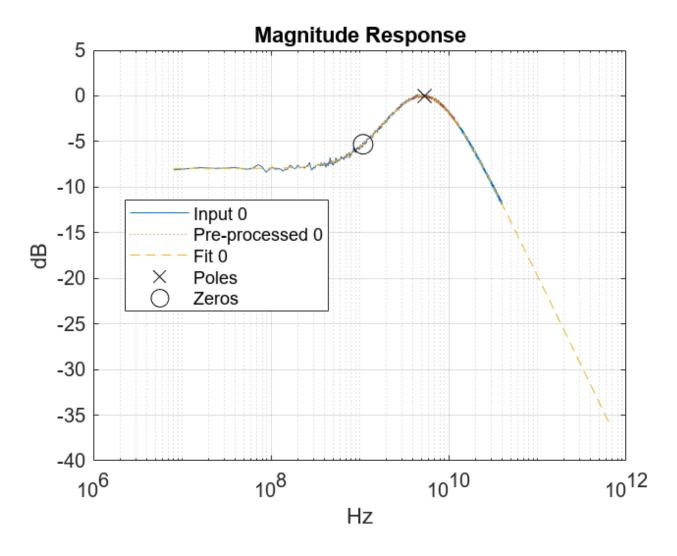

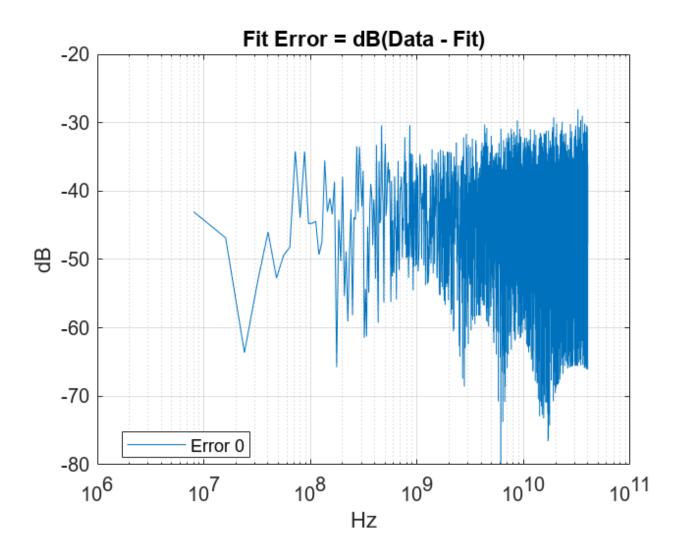

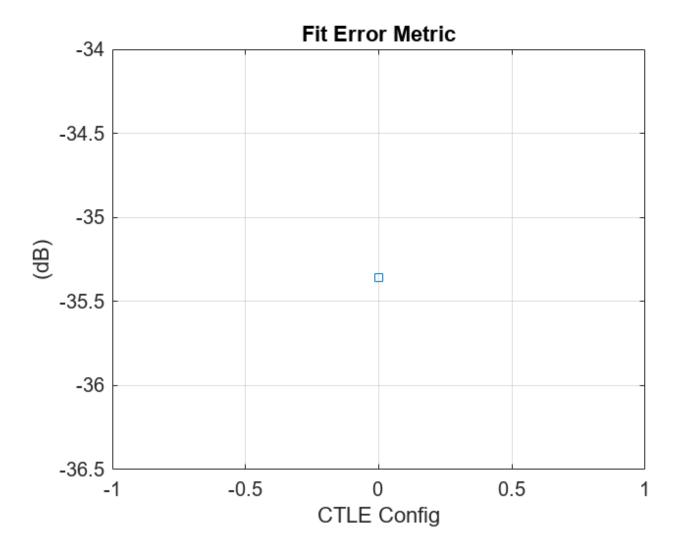

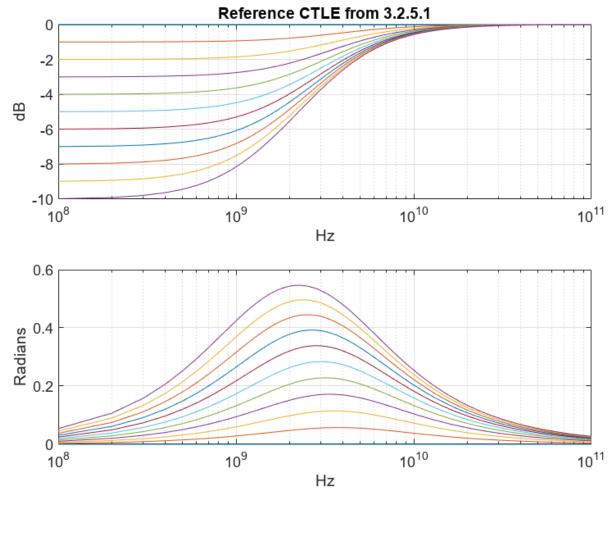

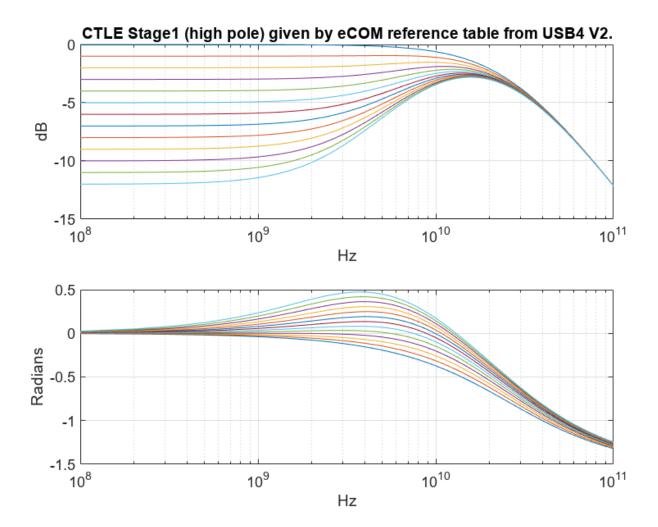

This example shows how to use the **CTLE Fitter** app to configure a CTLE block from SerDes Toolbox™ in the SerDes Designer app or in Simulink®. You can use the **CTLE Fitter** app to fit zeros, poles, and gains from a transfer function to create a GPZ Matrix and then export to your workspace. The **CTLE Fitter** app finds the GPZ Matrix by performing a fit comparison to a transfer function using the rational (RF Toolbox) function from RF Toolbox™.

#### **Using CTLE Fitter App**

You can open the CTLE Fitter app from SerDes Toolbox using any of the three workflows:

- From the CTLE block in the **SerDes Designer** app.

- From the CTLE block in the Simulink model.

- From the MATLAB® command window in the standalone mode.

#### **Configure CTLE Block in SerDes Designer App**

This workflow creates a variable representing a GPZ Matrix in the base workspace that is referenced by the CTLE block **GPZ properties** field in the **SerDes Designer** App. The steps are:

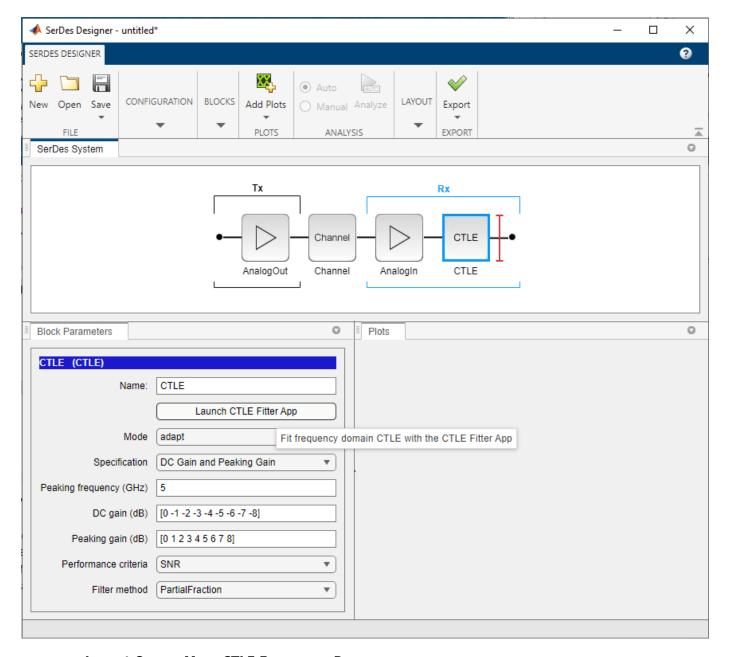

- Add a CTLE block and click the button **Launch CTLE Fitter App**.

- Import a CTLE frequency response. There can also be multiple responses in your data file.

- Adjust preprocess options for your transfer function data.

- Configure parameters of the rational function from RF Toolbox to optimize the fit to the transfer function.

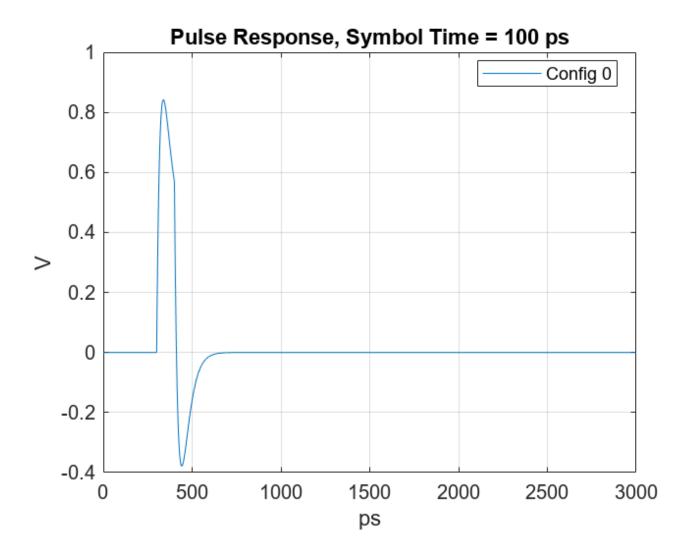

- Visualize the fit response within the CTLE Fitter app using plots provided for magnitude response and pulse response.

- Close the **CTLE Fitter** app and continue with your session in the **SerDes Designer** app.

#### Simulink SerDes Model with CTLE block

This workflow creates a variable representing a GPZ Matrix in the model workspace and references this in the CTLE block mask GPZ field. The steps are:

- Open the CTLE block mask and click the button **Launch CTLE Fitter App**.

- Import a CTLE frequency response.

- Adjust preprocess options for your transfer function data.

- Configure parameters of the rational function from RF Toolbox to optimize the fit to the transfer function.

- Visualize the fit response within the **CTLE Fitter** app using plots provided for magnitude response and pulse response.

- Close the **CTLE Fitter** app and continue with your session in Simulink.

#### **Standalone Mode**

This workflow creates a variable in the base workspace representing a GPZ Matrix. The steps are:

• Launch the app with the MATLAB command ctlefitter.

- Import a CTLE frequency response.

- Adjust preprocess options for your transfer function data.

- Configure parameters of the rational function from RF Toolbox to optimize the fit to the transfer function.

- Visualize the fit response within the **CTLE Fitter** app using plots provided for magnitude response and pulse response.

- You have the option to both export a script and save a GPZ Matrix to the base workspace.

- Close the CTLE Fitter app and continue with your session in MATLAB

#### **Configure CTLE Block in the SerDes Designer App**

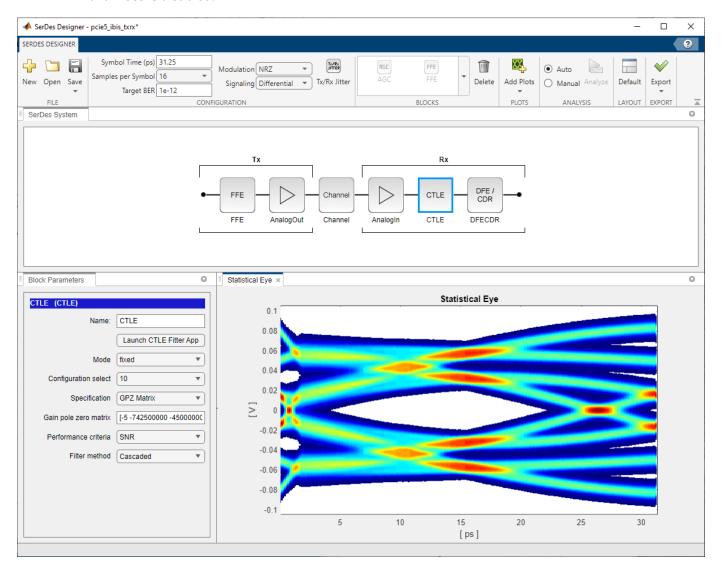

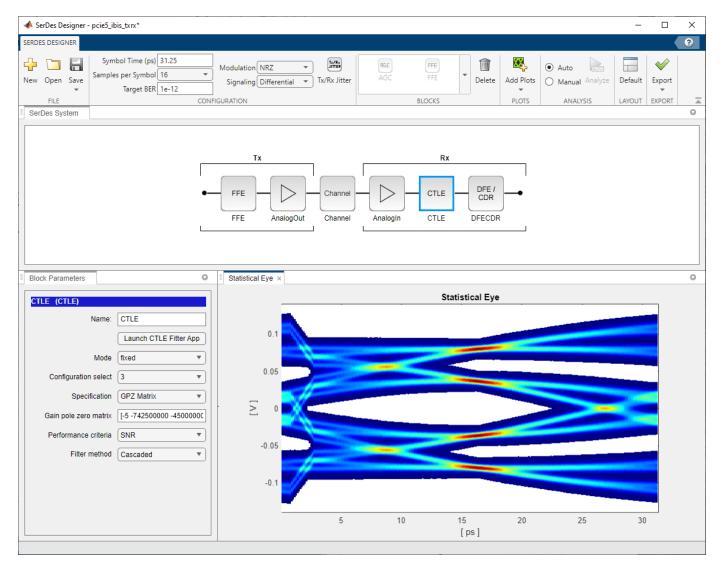

Launch the **SerDes Designer** app. Place a CTLE block after the analog model of the receiver. Then in the **Block Parameters** section, you can click on the button to launch the CTLE Fitter App.

#### **Import One or More CTLE Frequency Responses**

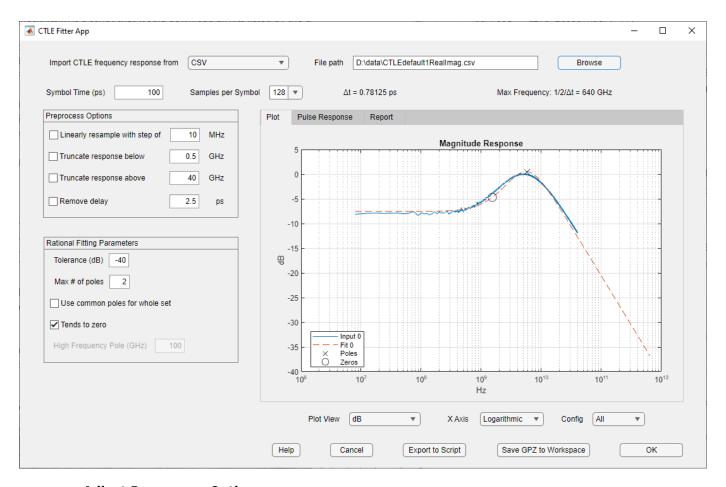

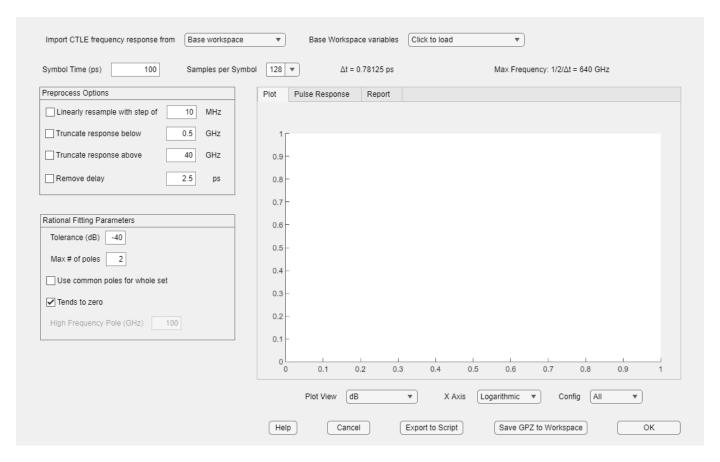

The app will open with some default values shown. Follow these steps to import a file containing one or more CTLE frequency responses:

- Click on the dropdown menu "Import CTLE frequency response from" and select the "CSV" option

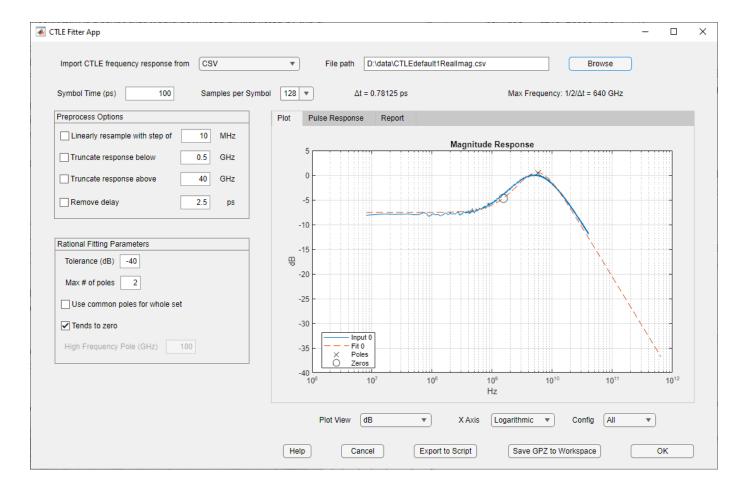

- Click the Browse button to open a .csv file containing a transfer function. **Note:** You can use the file attached to this example "CTLEdefault1RealImag.csv" to explore the features of the ctlefitter app. In the screenshots below, this file has been placed in the folder "D:\data" but may be in a different location on your system.

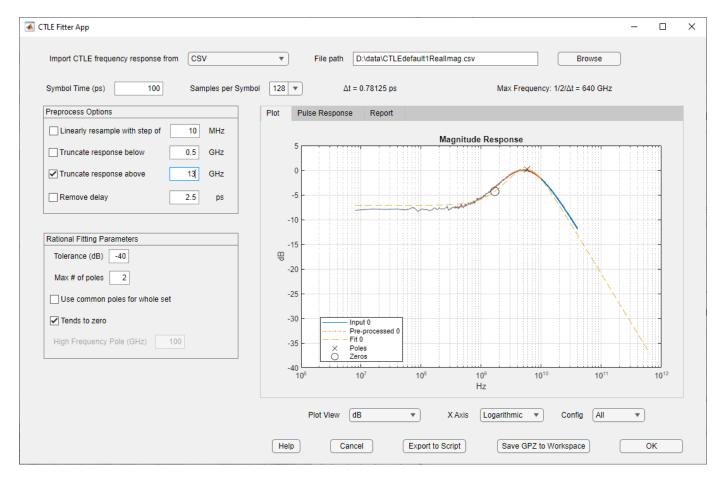

- You will see the app loads the file and automatically updates the figure shown on the Plot tab:

#### **Adjust Preprocess Options**

In the app, you can see many **Preprocess Options** are available. For example it is possible to truncate the data set from the transfer function used by the Fit. In the screenshot below you can see this is set to a cutoff frequency of 13 GHz:

You can also adjust:

- · Linearly resample with step size in MHz

- Truncate response below a specified frequency in GHz

- Truncate response above a specified frequency in GHz

- · Remove delay in picoseconds

#### **Configure Rational Fitting Parameters**

You can configure the way the MATLAB function rational determines a fit by adjusting the following:

- Error tolerance (dB)

- Maximum number of poles

- Use common poles for whole set

- Enable or disable "tends to zero"

These parameters are explained in the documentation for the MATLAB function rational, which is part of the RF Toolbox.

#### **Report on Rational Fit Results**

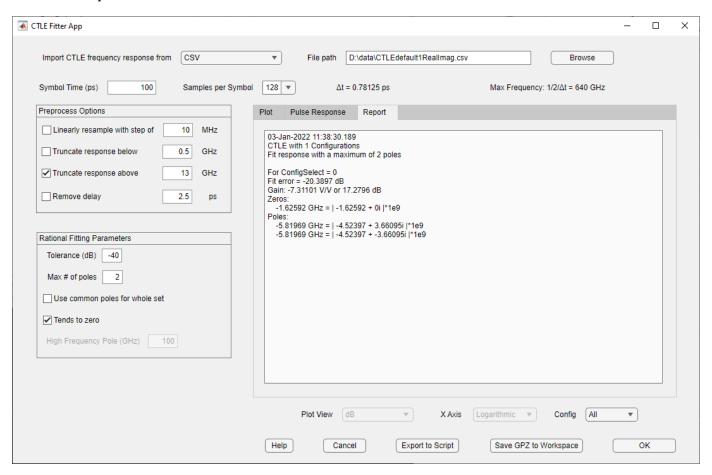

You can view the statistical parameters of the fit reported by the MATLAB function rational on the "Report" tab:

#### **Pulse Response**

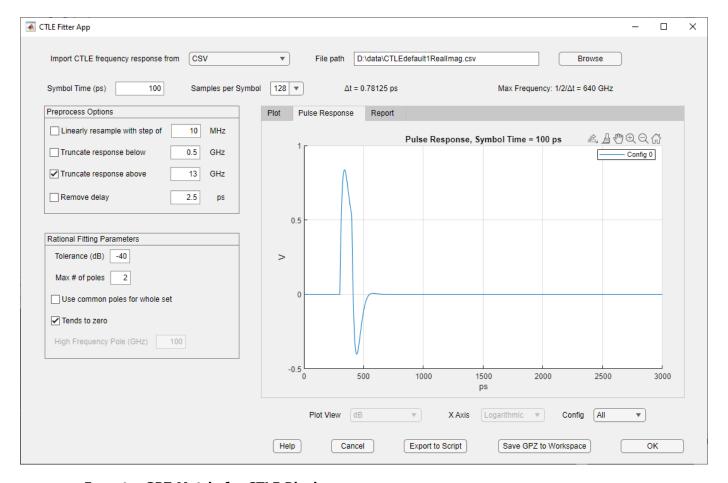

You can view the pulse response on the Pulse Response tab:

#### **Export a GPZ Matrix for CTLE Block**

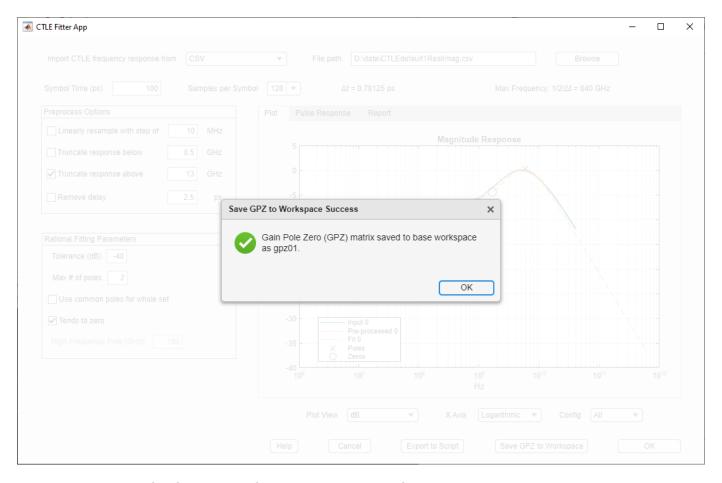

You can export the  $\ensuremath{\mathsf{GPZ}}$   $\ensuremath{\mathsf{Matrix}}$  to the Workspace by clicking on the button "Save  $\ensuremath{\mathsf{GPZ}}$  to Workspace."

**Note:** If you have previously exported a GPZ Matrix, the name will automatically increment. For example, gpz01 is created in the figure below, but if gpz01 already exists in the workspace it would be automatically named gpz02 and added to your workspace.

#### **Export Script from CTLE Fitter App to Base Workspace**

You can also export a script from the ctlefitter app to the base workspace by clicking on the button "Export to Script" and you can see example output below.

**Note:** The script contents you see may differ from the example below-depending on the data file being analyzed and your specific CTLE configuration options.

```

%Read in file:

fn = 'CTLEdefault1RealImag.csv';

[f,H]=ctlefit.readcsv(fn);

SymbolTime = le-10;

%Initialize ctleit object

obj = ctlefit(...

'f',f,...

'H',H,...

'SampleInterval',7.8125e-13,...

'MaxNumberOfPoles',2,...

'ErrorTolerance',-40,...

'TendsToZero',1,...

'UseCommonPoles',0,...

'PaddedPole',le+11);

```

```

%Preprocess transfer function waveform

df = 1e+07;

%resample(obj,df);

fcut1 = 5e+08;

%truncateBelow(obj,fcut1);

fcut2 = 1.3e+10;

truncateAbove(obj,fcut2);

delay = 2.5e-12;

%removeDelay(obj,delay);

%Get GPZ matrix

gpz = obj.GPZ;

%Visualize and create report

%TFView (Transfer function view) can be 'dB', 'Phase', 'Real/Imag',

%'Phase Delay', 'Group Delay'.

TFView = 'dB';

%ConfigSelect (CTLE Configuration Select) can be - 'All', 'Worst fit', 0 to

%N-1, where N is the number of configurations.

ConfigSelect = 'All';

%AxisStyle can be 'semilogx', 'plot', 'semilogy' or 'loglog'.

AxisStyle = 'semilogx';

figure,

plot(obj,TFView,ConfigSelect,AxisStyle)

```

figure,

plotPulse(obj,ConfigSelect,SymbolTime)

figure,

plotError(obj,ConfigSelect)

figure,

plotFitMetric(obj)

figure,

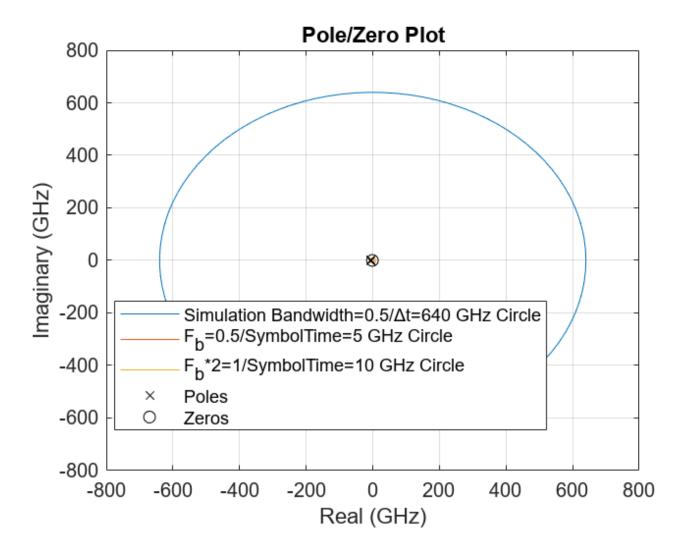

plotPoleZero(obj,ConfigSelect,SymbolTime)

#### **Simulink SerDes Model with CTLE block**

You can configure a Simulink SerDes Model with a CTLE block by opening the CTLE block parameters and click the "Launch CTLE Fitter App" button. You can follow the same steps outlined

above in the section Configure CTLE Block in the SerDes Designer App on page 4-3to configure the **CTLE Fitter** app and export a GPZ Matrix for use in a CTLE block.

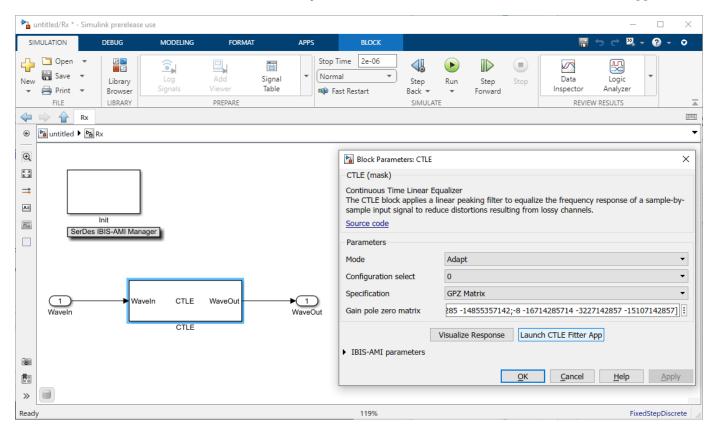

In the Block Parameters of the CTLE, you can click the button to launch the ctlefitter app:

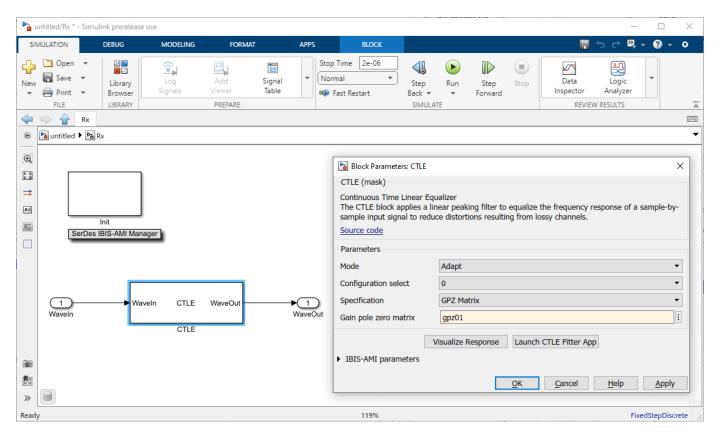

After you close the ctlefitter app, you will see the CTLE block is automatically configured to use the GPZ Matrix it created:

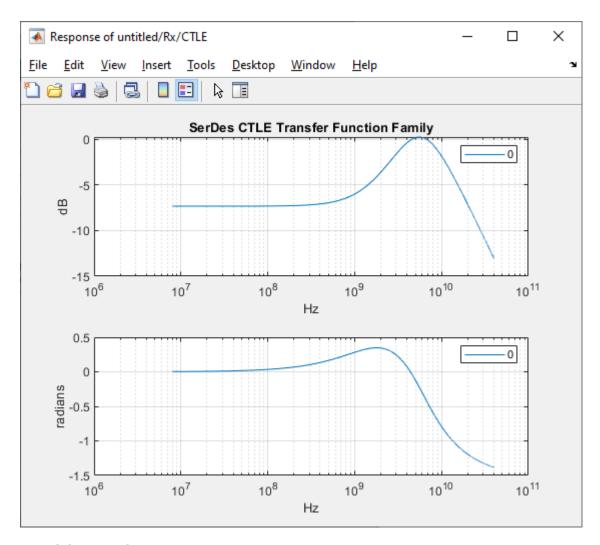

You can confirm the transfer function represented by the GPZ Matrix has a reasonable magnitude and phase response by clicking on "Visualize Response" button. These plots are also available in the SerDes Designer app workflow, and further detailed plots are provided as part of the exported script template.

#### **Standalone Mode**

Open the CTLE fitter app from the MATLAB command window: ctlefitter;

You can follow the same steps outlined above in the section Configure CTLE Block in the SerDes Designer App on page 4-3 to configure the **CTLE Fitter** app and export a GPZ Matrix to the base workspace in your MATLAB session.

Once you browse to and open a file containing one or more CTLE filter responses, you will see the app automatically updates the figure shown on the Plot tab:

#### **See Also**

**SerDes Designer** | CTLE | serdes.CTLE | rational

#### **More About**

• "Globally Adapt Receiver Components Using Pulse Response Metrics to Improve SerDes Performance" on page 4-27

# Convert Scattering Parameter to Impulse Response for SerDes System

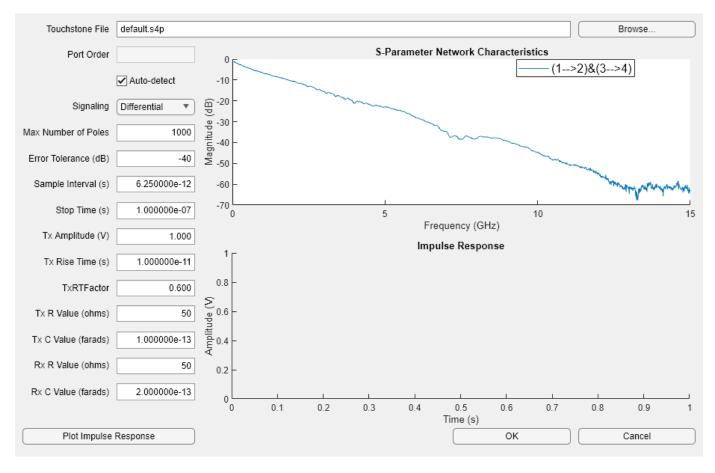

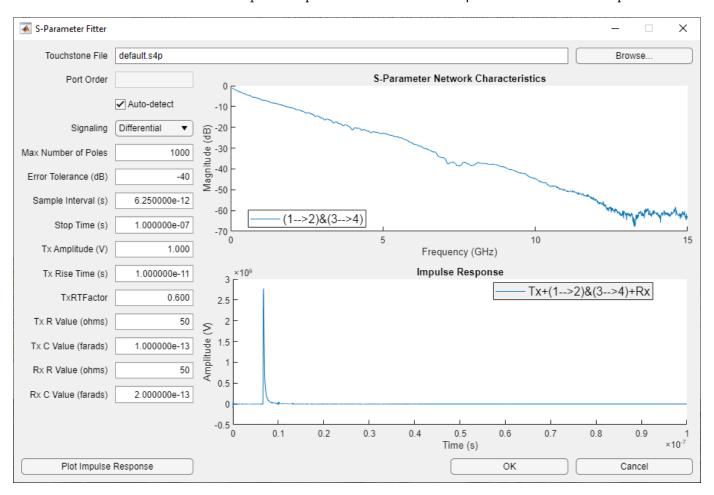

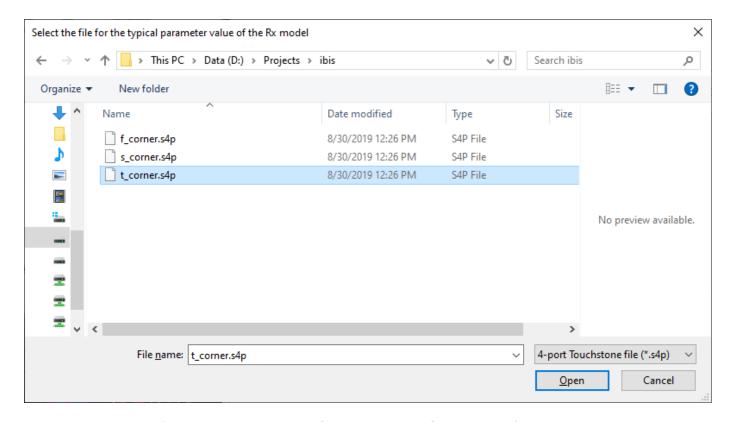

This example shows how to find an Impulse Response by combining a Scattering-Parameter (S-Parameter) model of a baseband communication channel along with a transmitter and receiver represented by their analog characteristic impedance values. You will see how to find an Impulse Response of this network using the sParameterFitter app to create an SParameterChannel (hyperlink to sParameterChannel in doc) object in SerDes Toolbox $^{\text{\tiny TM}}$ , which also uses some supporting functions from RF Toolbox $^{\text{\tiny TM}}$  such as rational (RF Toolbox) and impulse (RF Toolbox).

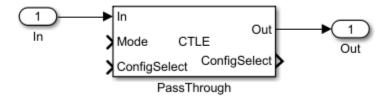

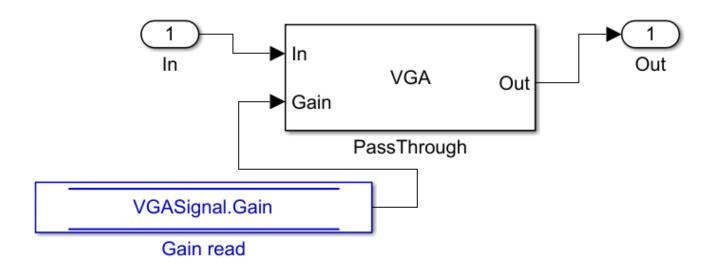

#### **Configure Variables**